### Application Note AN96081

### Abstract

Picture-in-Picture Controller SAB 9076 with colour decoders TDA 8315, TDA8310A and video processor TDA 4780.

This application note describes the possible configurations of the PiP-Controller environment, a rough description of the PiP-controller itself, the IIC-Bus registers and their controlling, a stand-alone evaluation boardset and gives some application advice.

Purchase of Philips  $I^2C$  components conveys a license under the Philips  $I^2C$  patent to use the components in the  $I^2C$  system, provided the system conforms to the  $I^2C$  specifications defined by Philips.

### © Philips Electronics N.V. 1997

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Application Note AN96081

### **APPLICATION NOTE**

### System Application of SAB 9076/77 PiP Processor

### AN96081

### Author(s):

Eckhard Bruns Product Concept & Application Laboratory Hamburg Germany

### Keywords

Multi standard PiP Picture-in-Picture Concepts SAB 9076/77 TDA 8315 TDA 8310A TDA 4780 PiP\_O

Date: 02.08.1996

### Application Note AN96081

### Summary

This application note describes some concepts to built in a PiP function in environments like TV-sets, Video recorders or satellite receivers. The proposals for implementing such a PiP application are shown and discussed in the chapter 2. Several conceptional aspects are taken into account.

The PiP controller itself is roughly described in chapter 3. For more detailed informations please refer to the application notes [5] and [6].

The major part of this application note, chapter 4, explains the PiP evaluation boardset in detail. The used IC's TDA 8315T, TDA 8310A and TDA 4780 are shown and explained in detail if necessary. The schematics are discusses in detail and application hints are given, too.

Because of the PiP evaluation boardset is designed as a modular system, the interfaces between the modules are described signal by signal with their characteristics. The layouts of the modules are attached.

I hope the user of our PiP evaluation boardset and this application note finds all the informations he wishes to know.

Special thanks I like to give to my colleagues in Nijmegen for their very good support.

Hamburg, in August 1996

Eckhard Bruns

### Application Note AN96081

### CONTENTS

| 1. | Introdu                                    | ction                                             |                                                                                                                                                                                                                                                                                                                                                                            |                                       |                                       |                                                 |                                                    |                                           | 9                                                                                                                                                                                                                                                                                                                      |

|----|--------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|-------------------------------------------------|----------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | Archite<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Two chan<br>Three cha<br>Applicatio<br>Applicatio | everal PiP-applicationsnel applications in 50Hz domainunnel application in 50Hz domainns for 100Hz - TV - conceptsns for VCR - conceptsns for SAT - Receivers                                                                                                                                                                                                              | · · ·                                 | <br><br>                              | · ·<br>· ·<br>· ·                               | · ·<br>· ·<br>· ·                                  | · · · · · · · · · · · · · · · · · · ·     | 10<br>12<br>14<br>15                                                                                                                                                                                                                                                                                                   |

| 3. | Short I<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Blockdiag<br>Descriptio<br>PiP mode<br>Backgrour  | of the PiP-Controller SAB 9076/77                                                                                                                                                                                                                                                                                                                                          | · · ·                                 | · · · ·                               | · ·<br>· ·<br>· ·                               | · ·<br>· ·<br>· ·                                  | · · · · · · · · · · · · · · · · · · ·     | 24<br>25<br>26<br>28                                                                                                                                                                                                                                                                                                   |

| 4. | Descrij<br>4.1<br>4.2                      | NTSC Col<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4      | PiPO - Boardset                                                                                                                                                                                                                                                                                                                                                            | · · · · · · · · · · · · · · · · · · · |                                       |                                                 |                                                    |                                           | <ul> <li>34</li> <li>34</li> <li>34</li> <li>35</li> <li>37</li> <li>38</li> <li>40</li> <li>40</li> <li>40</li> <li>41</li> <li>42</li> <li>43</li> <li>44</li> <li>44</li> <li>45</li> </ul> |

|    |                                            | 4.2.2                                             | RGB - Multiplexer       Sync pulse generation         Description of the multistandard decoder module H5VS48       General         Inputs       Inputs         Inputs       Inputs         IC controls       Inputs         Handshake communication between TDA 8310A and TDA 8395         Loop Filters       Crystals         Colour standard indication       Decoupling |                                       | · · · · · · · · · · · · · · · · · · · | · · ·<br>· ·<br>· ·<br>· ·<br>· ·<br>· ·<br>· · | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · ·<br>· · · | · · ·<br>· · ·<br>· · ·<br>· · ·<br>· · · | 48<br>49<br>54<br>54<br>54<br>54<br>55<br>56<br>56<br>56<br>56                                                                                                                                                                                                                                                         |

# System Application of SAB 9076/77 PiP Processor

# Application Note AN96081

|    |         |            | Supply                                                           |

|----|---------|------------|------------------------------------------------------------------|

|    |         | 4.2.3      | Interface, Probing and Adjustments                               |

|    |         | 4.2.4      | Layout and Placement                                             |

|    |         | 4.2.5      | Application hints.                                               |

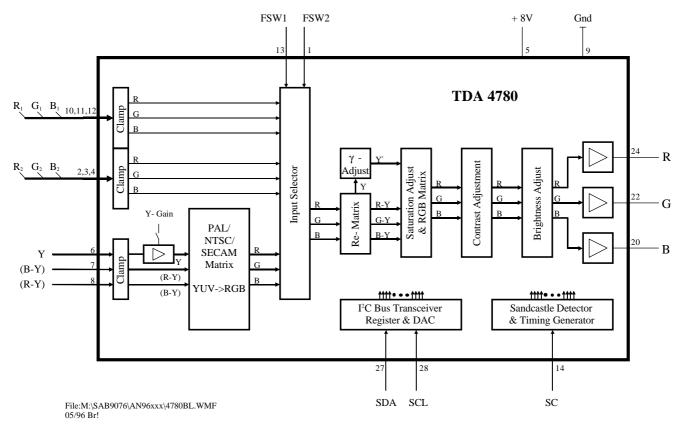

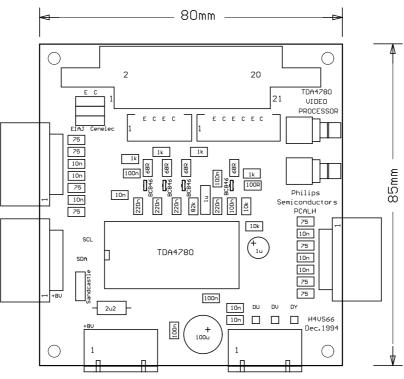

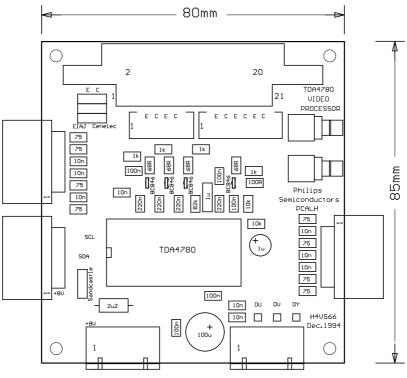

|    | 4.3     | Videoproc  | essor TDA 4780 on H5VS66                                         |

|    |         | 4.3.1      | Description of TDA 4780                                          |

|    |         |            | General description                                              |

|    |         |            | General description                                              |

|    |         |            | Video processing path                                            |

|    |         |            | Timing and controlling.                                          |

|    |         | 4.3.2      | Description of I <sup>2</sup> C-Bus registers and default values |

|    |         |            | Description of I <sup>2</sup> C-Bus registers                    |

|    |         |            | I <sup>2</sup> C bus register for video signal adjusting         |

|    |         |            | Control register                                                 |

|    |         |            | Default values for the $I^2C$ bus register                       |

|    |         | 4.3.3      | Description of the video processor module H4VS66                 |

|    |         |            | General                                                          |

|    |         |            | Inputs                                                           |

|    |         |            |                                                                  |

|    |         |            | IC controls.                                                     |

|    |         |            | Further application hints for TDA 4780                           |

|    |         |            | Supply                                                           |

|    |         | 4.3.4      | Interface and Probing                                            |

|    |         | 4.3.5      | Layout and Placement                                             |

|    |         | 4.3.6      | Application hints.                                               |

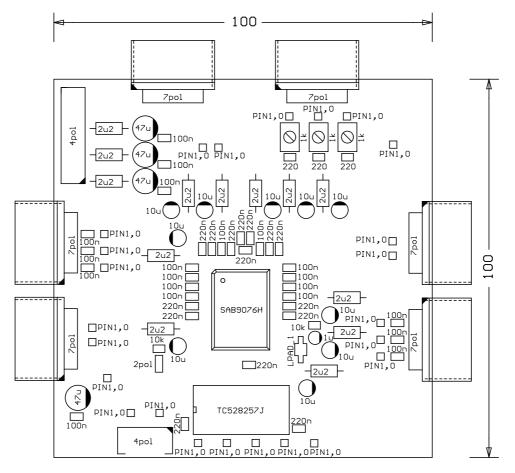

|    | 4.4     | PiP Contro | Dller SAB 9076/77 on H6VS01                                      |

|    |         | 4.4.1      | Description of the Main module H6VS01                            |

|    |         |            | General                                                          |

|    |         |            | Inputs                                                           |

|    |         |            | Outputs                                                          |

|    |         |            | IC controls                                                      |

|    |         |            | Supply                                                           |

|    |         |            | Further application hints.                                       |

|    |         | 4.4.2      | Interface and Probing                                            |

|    |         | 4.4.3      | Layout and Placement                                             |

| 5. | Applier | tion hints |                                                                  |

| -  | ••      |            |                                                                  |

| 6. | Refere  | nces       |                                                                  |

| 7. | Notes   |            |                                                                  |

### Application Note AN96081

### List of figures

| Fig.1  | Two channel PiP-application in a 50Hz domain                                        | 10 |

|--------|-------------------------------------------------------------------------------------|----|

| Fig.2  | Three channel PiP-application in a 50Hz domain                                      |    |

| Fig.3  | extended three channel PiP-application in a 50Hz domain                             |    |

| Fig.4  | PiP signal processing in 100Hz TV concepts inserting the PiP signals on 50Hz domain | 14 |

| Fig.5  | Video signal processing in VCR - concept                                            |    |

| Fig.6  | First implementation of PiP signal processing into a VCR - concept                  |    |

| Fig.7  | Second implementation of PiP signal processing into a VCR - concept                 |    |

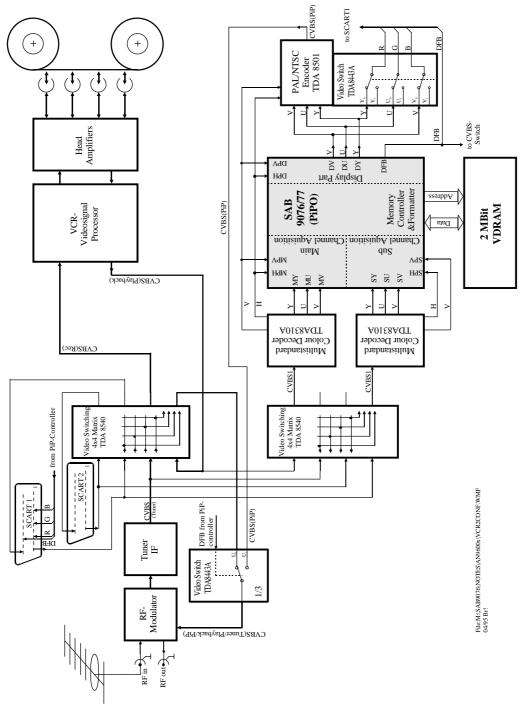

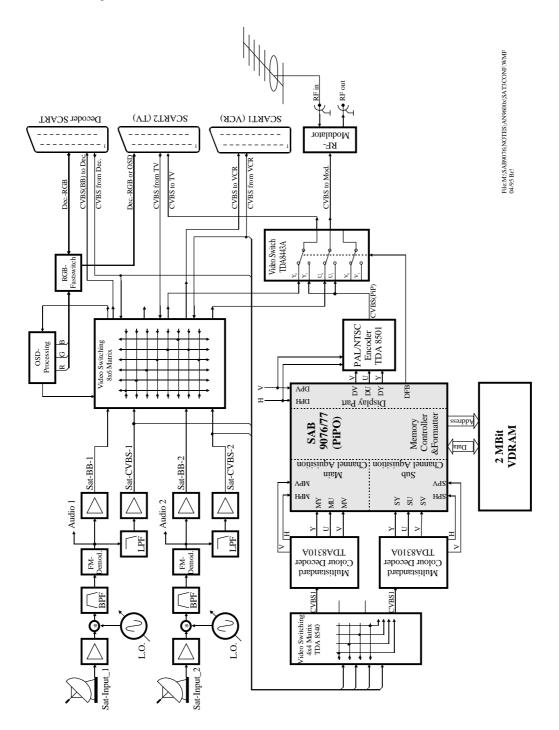

| Fig.8  | Blockdiagram of Twin-Satellite receiver                                             |    |

| Fig.9  | Simple implementation of PiP signal processing in an SAT-receiver concept           |    |

| Fig.10 | Extended application of PiP signal processing in an SAT-receiver concept            |    |

| Fig.11 | High end application of PiP signal processing in a SAT-receiver concept             |    |

| Fig.12 | Top shell block diagram of the PiP controller SAB 9076/77                           |    |

| Fig.13 | Pip modes 1                                                                         |    |

| Fig.14 | Pip modes 2                                                                         |    |

| Fig.15 | Background and PiP positioning                                                      |    |

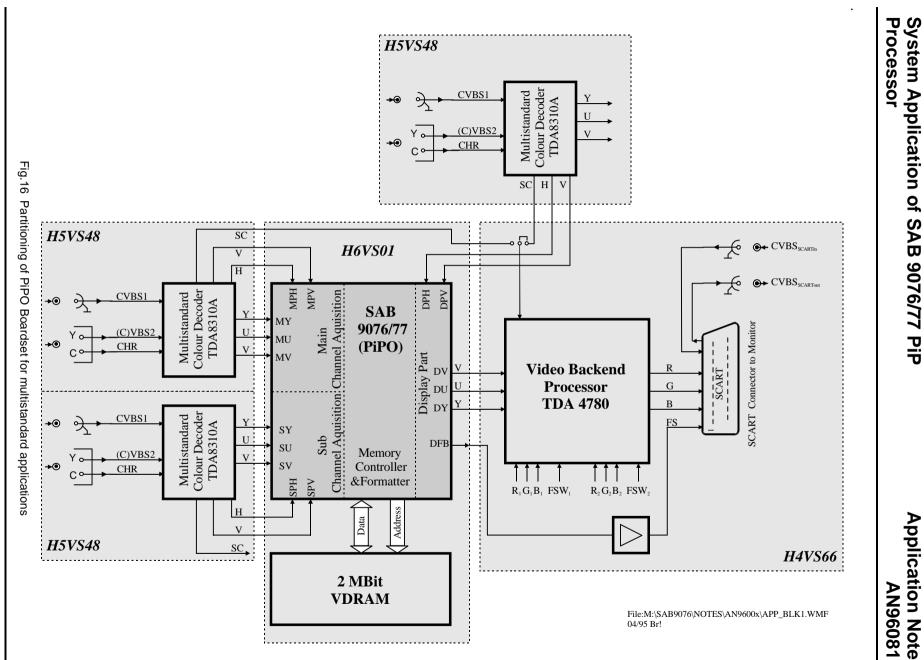

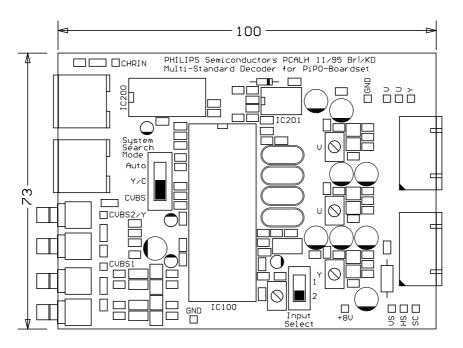

| Fig.16 | Partitioning of PiPO Boardset for multistandard applications                        |    |

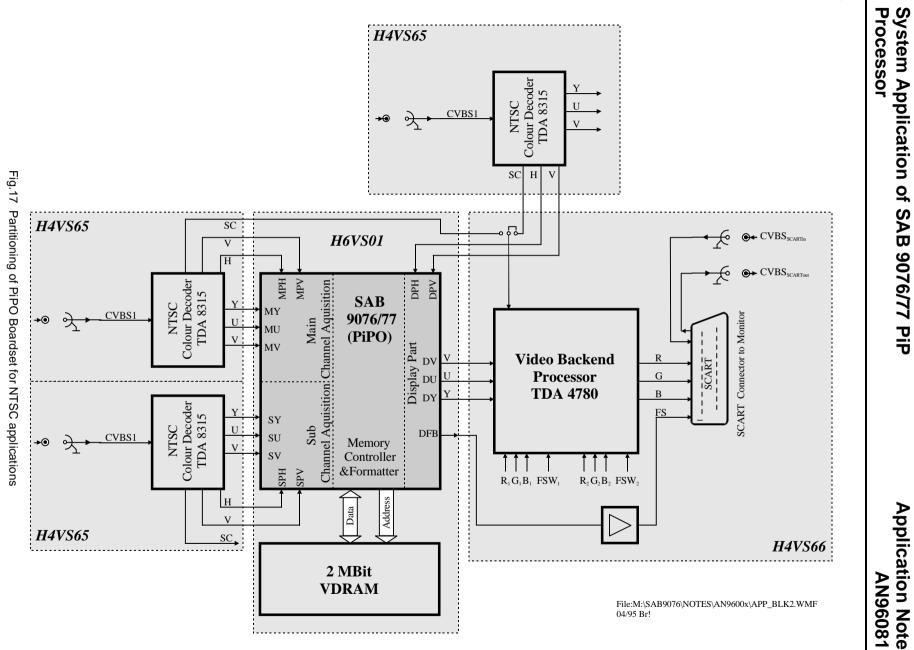

| Fig.17 | Partitioning of PiPO Boardset for NTSC applications.                                |    |

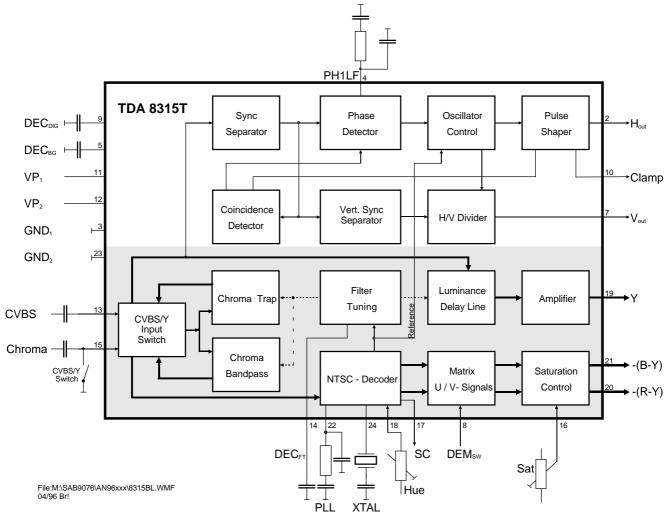

| Fig.18 | TDA8315: Blockdiagram of colour decoder with sync processor.                        |    |

| Fig.19 | HUE Control curve for TDA 8315T                                                     |    |

| Fig.20 | SAT Control curve for TDA 8315T                                                     |    |

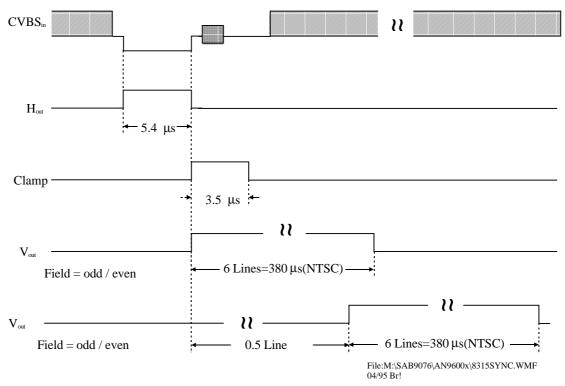

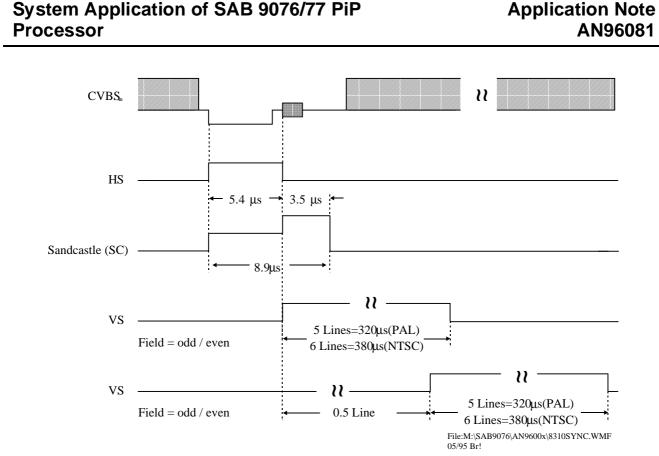

| Fig.21 | TDA8315: Timing of generated sync signals                                           |    |

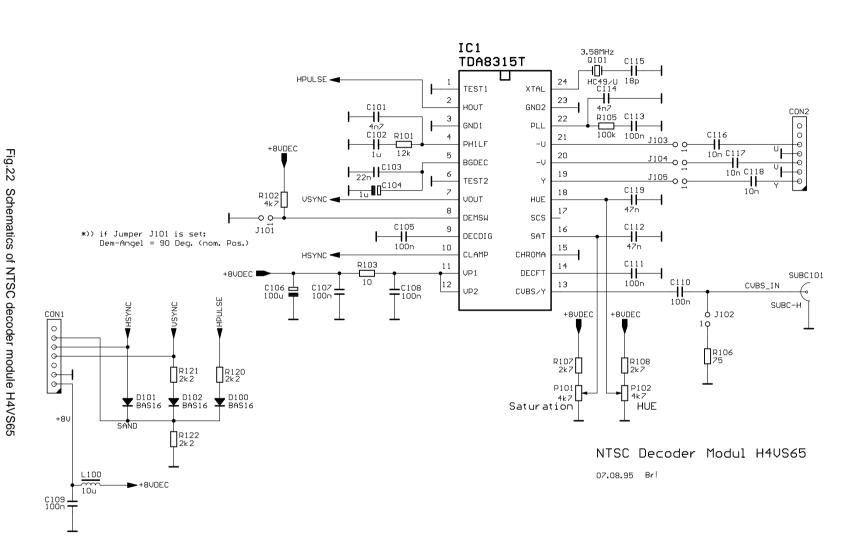

| Fig.22 | Schematics of NTSC decoder module H4VS65                                            |    |

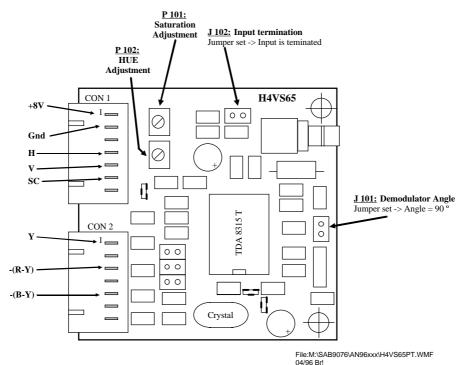

| Fig.23 | Relevant signals, settings and adjustments of H4VS65                                |    |

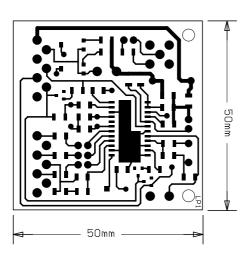

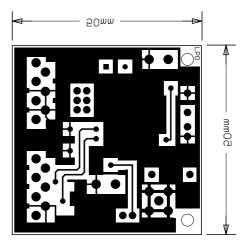

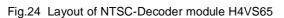

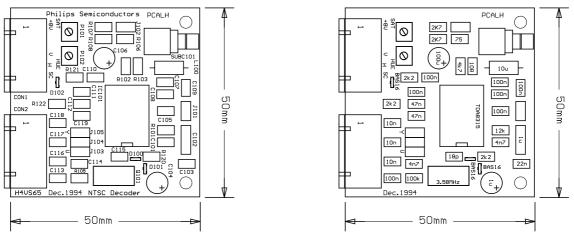

| Fig.24 | Layout of NTSC-Decoder module H4VS65                                                |    |

| Fig.25 | Components of NTSC-Decoder module H4VS65                                            |    |

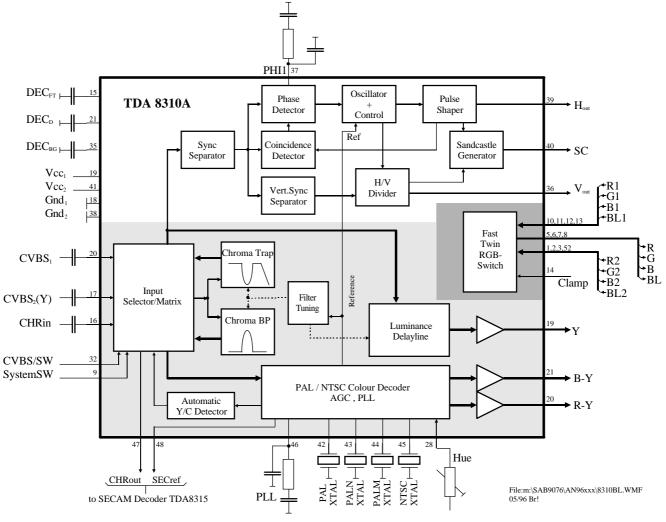

| Fig.26 | Blockdiagram of multistandard colour decoder TDA 8310A                              |    |

| Fig.27 | HUE control curve for TDA 8310A                                                     |    |

| Fig.28 | TDA8310A: Timing of generated sync signals                                          |    |

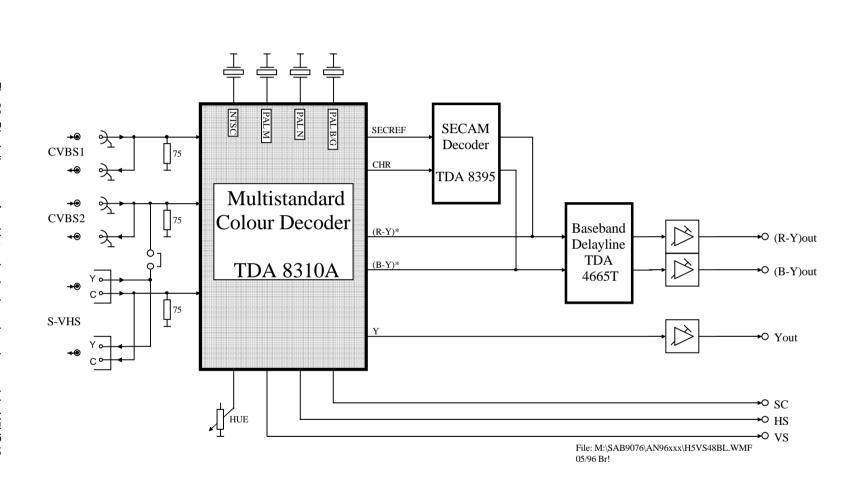

| Fig.29 | Blockdiagram of multistandard colour decoder module H5VS48                          |    |

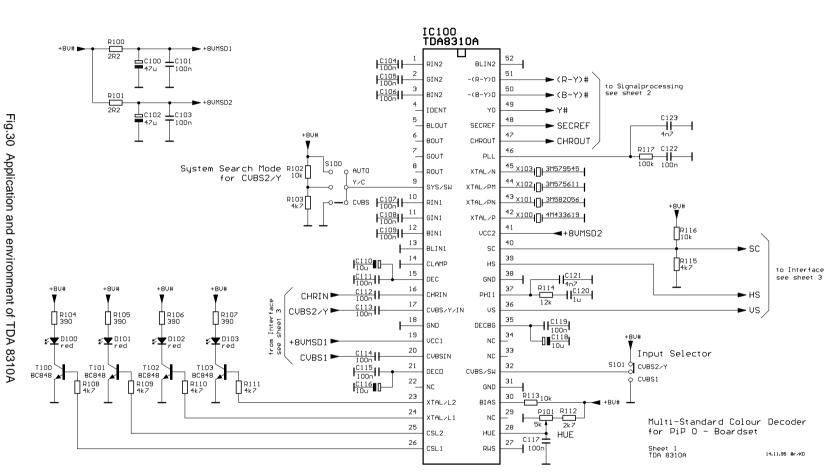

| Fig.30 | Application and environment of TDA 8310A                                            |    |

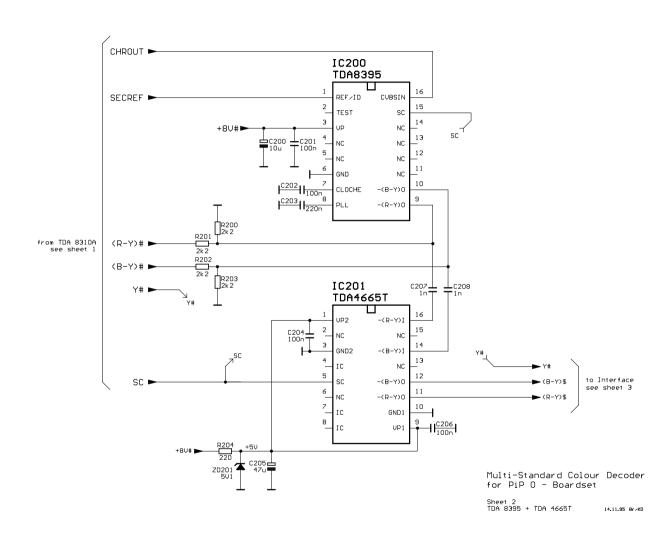

| Fig.31 | SECAM decoder TDA 8395 and baseband delayline TDA 4665T                             |    |

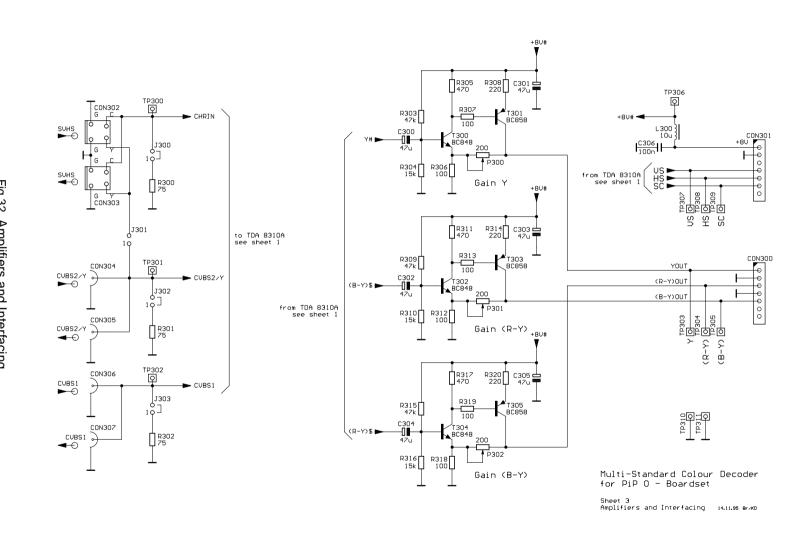

| Fig.32 | Amplifiers and Interfacing.                                                         |    |

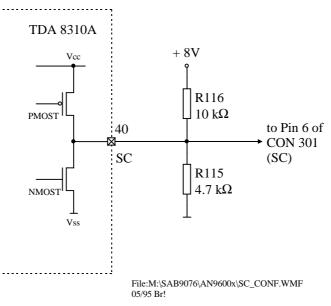

| Fig.33 | Output configuration of SC pin (TDA 8310A)                                          |    |

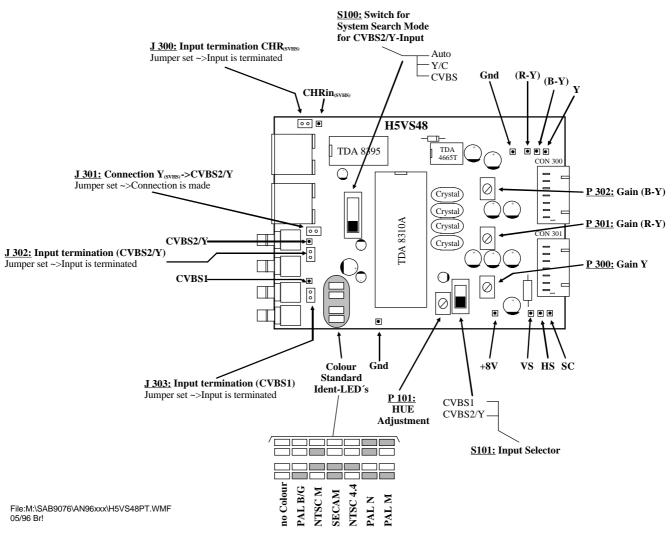

| Fig.34 | Relevant signals, settings and adjustments of H5VS48                                |    |

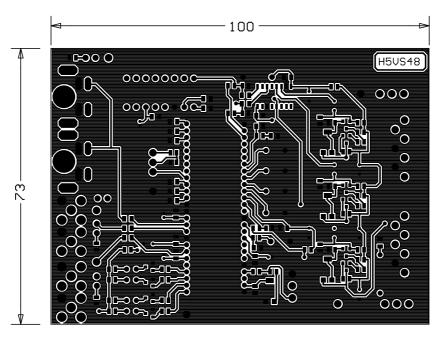

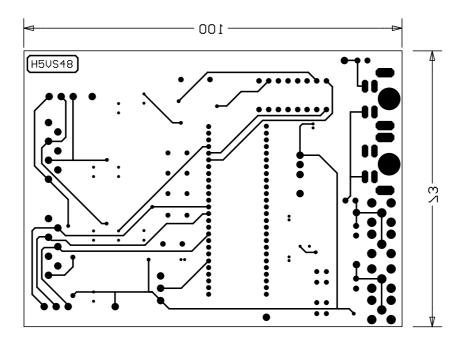

| Fig.35 | Layout of H5VS48 Topside                                                            |    |

| Fig.36 | Layout of H5VS48 Bottomside                                                         |    |

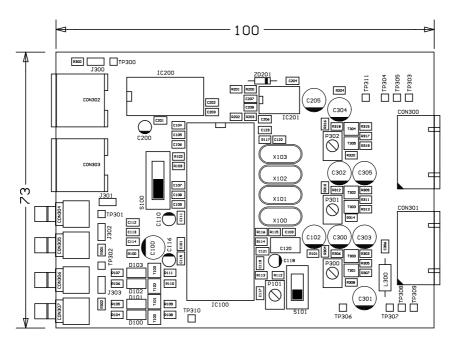

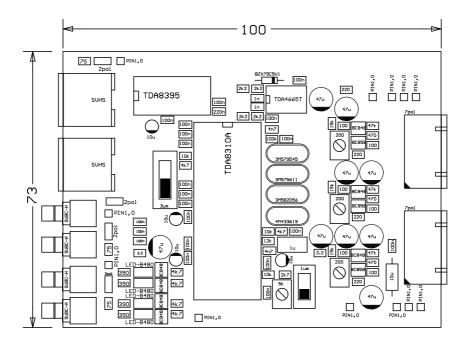

| Fig.37 | Placement of Topside - Components                                                   |    |

| Fig.38 | Values of Topside - Components                                                      |    |

| Fig.39 | Topside - Printing                                                                  | 62 |

| Fig.40 | Blockdiagram of Videoprocessor TDA 4780                                             | 63 |

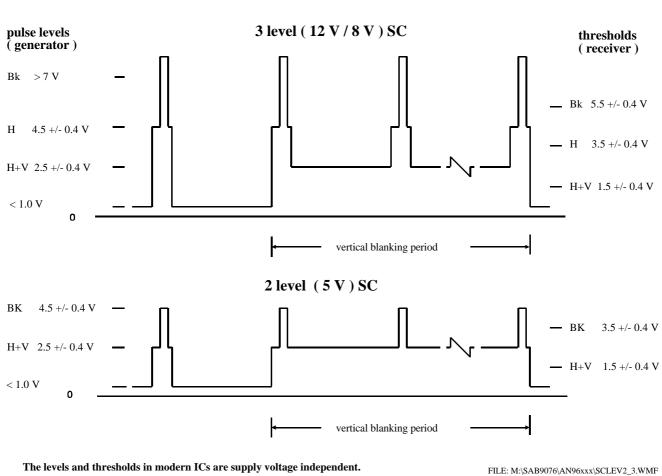

| Fig.41 | Signal forms and thresholds of two- and three level sandcastle pulses               | 65 |

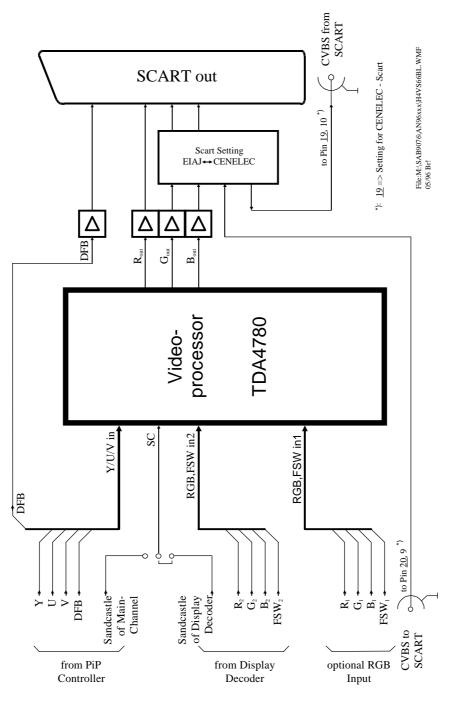

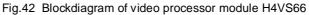

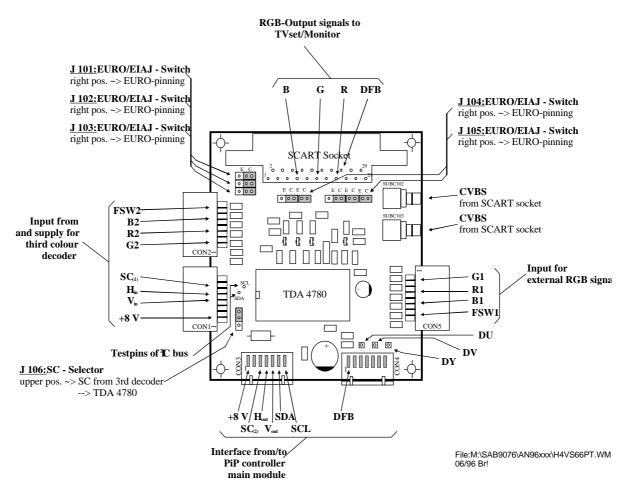

| Fig.42 | Blockdiagram of video processor module H4VS66                                       |    |

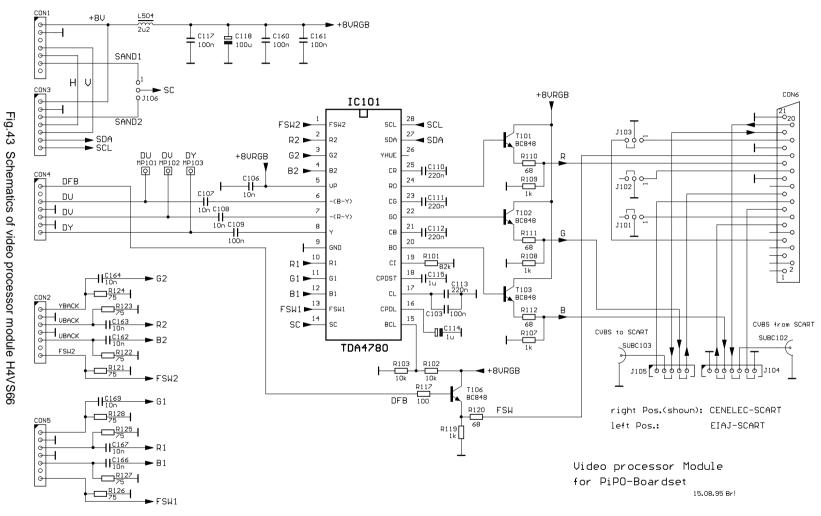

| Fig.43 | Schematics of video processor module H4VS66                                         | 72 |

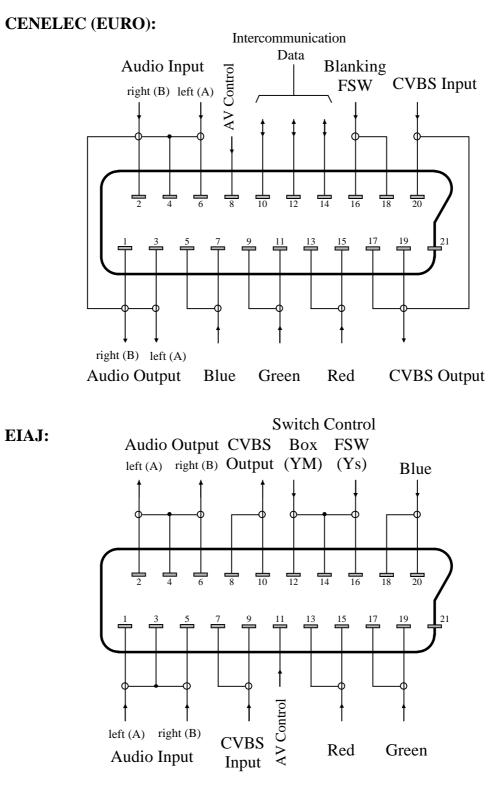

| Fig.44 | Pinning of SCART connectors                                                         |    |

| Fig.45 | Relevant signals and settings of H4VS66                                             | 77 |

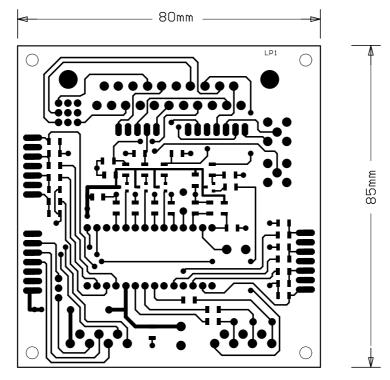

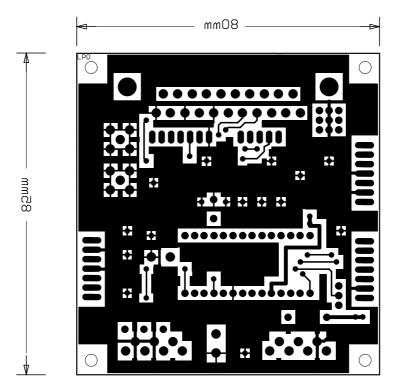

| Fig.46 | Layout of the H4VS66 Topside                                                        | 80 |

| Fig.47 | Layout of H4VS66 Bottomside                                                         | 80 |

### Application Note AN96081

| Fig.48 | Placement of Topside Components               | 1 |

|--------|-----------------------------------------------|---|

| Fig.49 | Values of Topside Components                  | 1 |

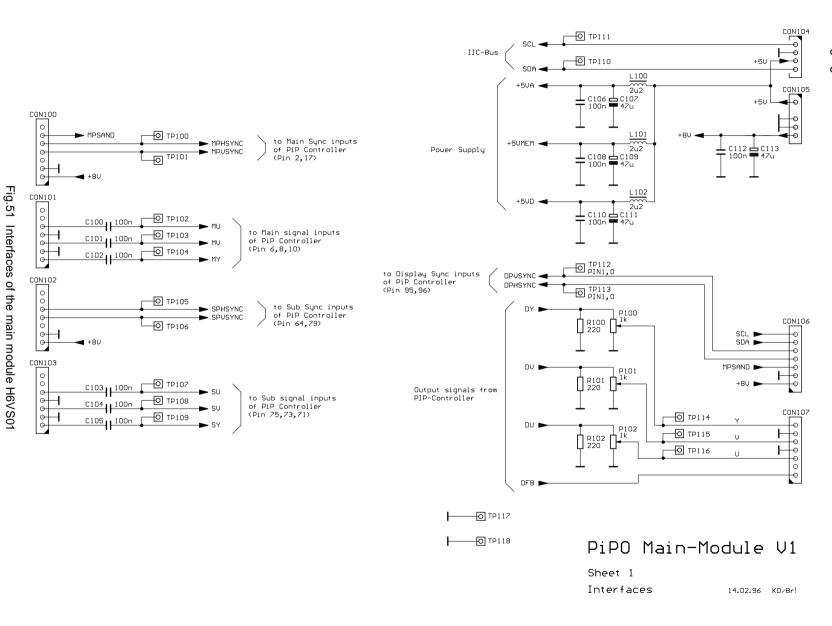

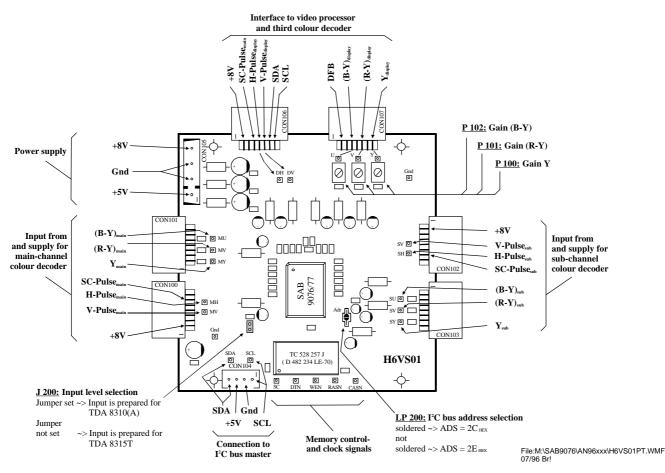

| Fig.50 | Blockdiagram of the main module H6VS01        | 2 |

| Fig.51 | Interfaces of the main module H6VS01          | 3 |

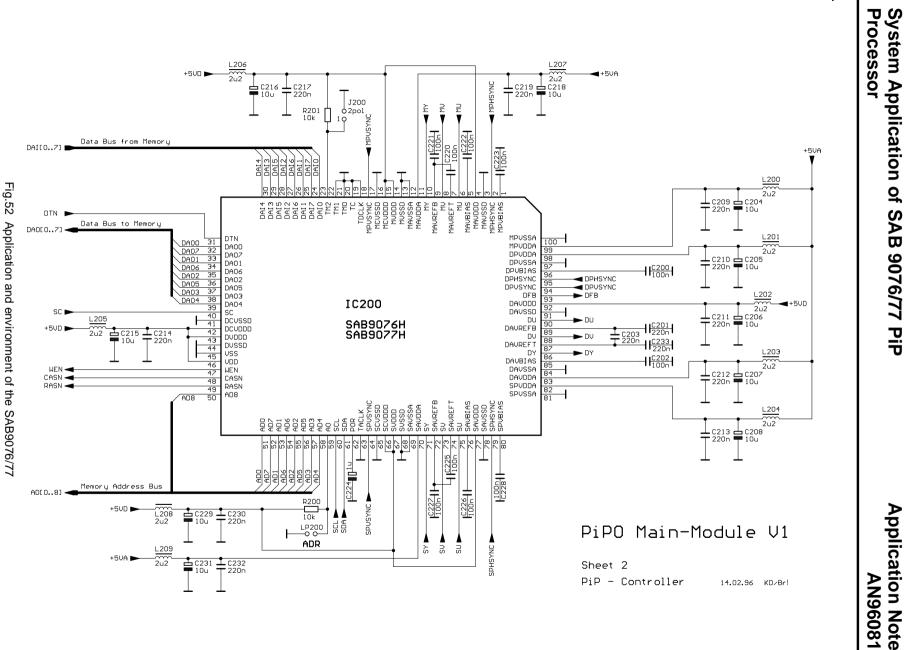

| Fig.52 | Application and environment of the SAB9076/77 | 4 |

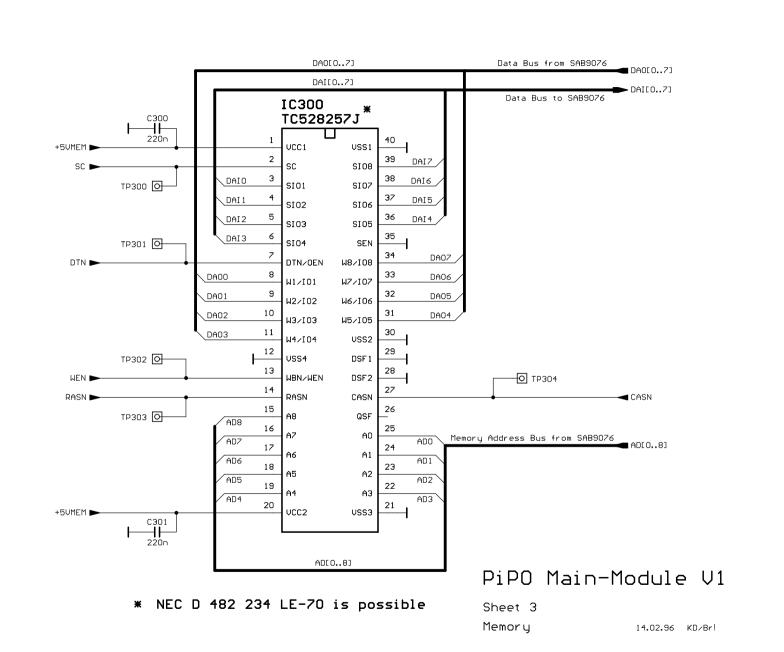

| Fig.53 | Application and environment of the Memory IC  | 5 |

| Fig.54 | Relevant signals and settings of H6VS01       | 0 |

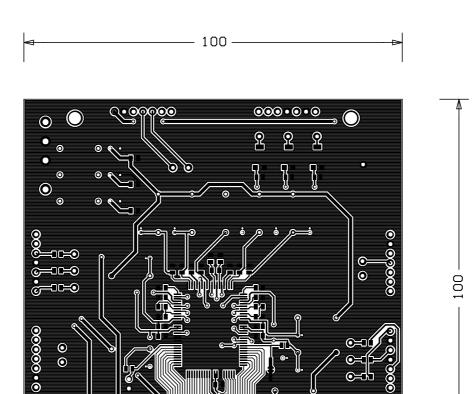

| Fig.55 | Layout of the H6VS01 Topside                  | 3 |

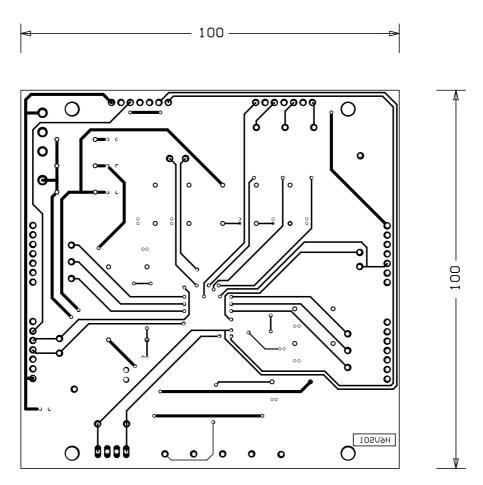

| Fig.56 | Layout of the H6VS01 Bottomside               | 4 |

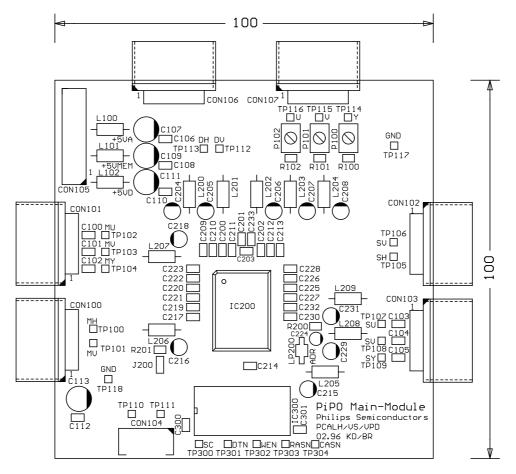

| Fig.57 | Placement of Topside - Components             | 5 |

| Fig.58 | Values of Topside - Components                | 6 |

### List of tables

| Pixels and Lines of PiP in respect to desired reduction                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIP Modes and presettings                                                                                                                                                                                           |

| Abbreviation of standard PiP modes                                                                                                                                                                                  |

| Overview of $I^2C$ bus registers for normal operation modes                                                                                                                                                         |

| Overview of additional I <sup>2</sup> C bus registers for manual mode                                                                                                                                               |

| Demodulator Angle Setting by Jumper J101                                                                                                                                                                            |

| Characteristics of Interface-signals                                                                                                                                                                                |

| Crystals for Multistandard Colour Decoder TDA 8310A                                                                                                                                                                 |

| Used Crystals on H5VS48 for TDA 8310A                                                                                                                                                                               |

| Indication of recognized colour standards                                                                                                                                                                           |

| Characteristics of Interface-signals                                                                                                                                                                                |

| Input signal selection                                                                                                                                                                                              |

| $I^2C$ bus register of TDA 4780                                                                                                                                                                                     |

| Control register 1 of TDA 4780                                                                                                                                                                                      |

| Control register 2 of TDA 4780                                                                                                                                                                                      |

| Signal input selection by the fast switches and the $I^2C$ bus register bits $\ldots \ldots \ldots$ |

| Control register 3 of TDA 4780                                                                                                                                                                                      |

| Default settings of TDA 4780 for PiP application                                                                                                                                                                    |

| Pins and signals to be switched                                                                                                                                                                                     |

| Characteristics of Interface-signals                                                                                                                                                                                |

| Setting of I <sup>2</sup> C bus address for SAB 9076/77                                                                                                                                                             |

| Input level adaption of SAB 9077                                                                                                                                                                                    |

| Characteristics of Interface-signals                                                                                                                                                                                |

|                                                                                                                                                                                                                     |

### **Application Note** AN96081

### 1. Introduction

Today the variety of TV-programs is growing nearly from day to day.

The software comes from several sources like the well known terrestrial broadcaster, cable systems, satellites, VCRs or security systems for example. But most the times only one TV-set with a large display is available at home.

So it's a clever solution to reduce the picture size of the interesting programs to 1/4 or 1/16 of the whole screen size and display it simultaneously with the main program.

For getting an overview of the actual running programs it is helpful to use the PiP concept as a program-searchtool. Together with the appropriate control-software its possible to divide the whole screen into 16 small pictures and fill each with a frozen picture of one of 16 several sources.

The device SAB9076/77 itself is able to handle two independent life pictures. Together with a fast switch it is possible to display two life pictures on a life background. The programs itself could be coded in different standards, PAL and NTSC for example. In fact a standard conversion is possible.

The device contains two independent acquisition channels incl. ADCs and data reduction and one display channel which contains the controlling of the external memory and the DACs.

The whole IC is controllable via IIC-bus.

The following application note first shows and explains several PiP-concepts in the 50Hz and 100Hz domain in part 2. Part 3 contains the roughly description of the PiP controller SAB9076/77 and how to control the device. Part 4 describes one of the possible applications. The chosen application is the stand-alone demoboard application. Part 5 gives some application hints for designing a PCB for the SAB9076/77.

### Application Note AN96081

### 2. Architectures of several PiP-applications

This chapter could give you an overview, what a wide range of possible applications for the PiPO-system exists. The following application proposals show the most interesting concepts, but the list must not be complete.

### 2.1 Two channel applications in 50Hz domain

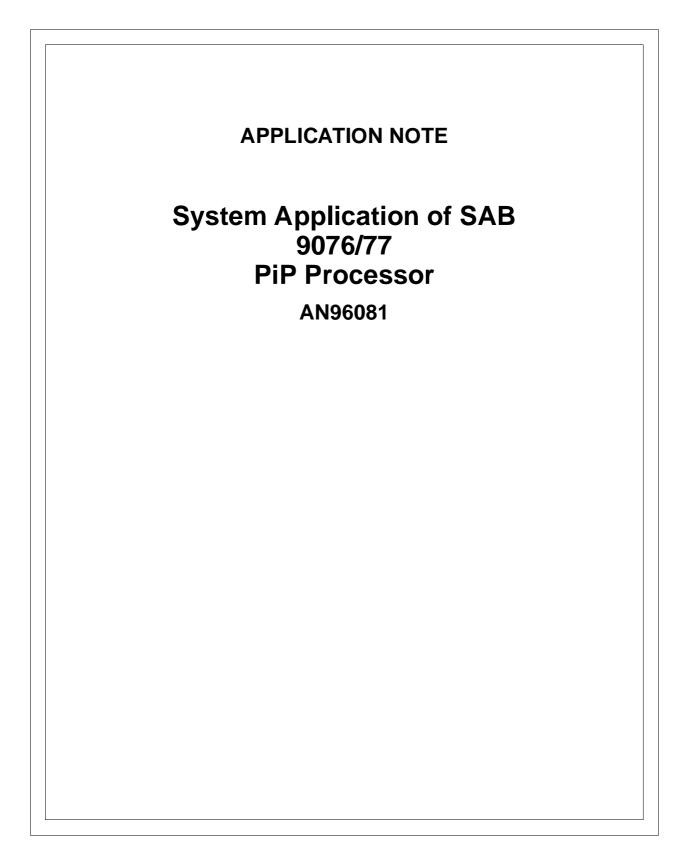

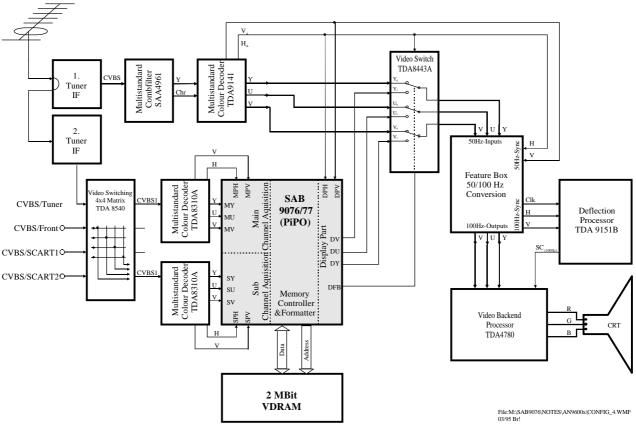

The main blocks for a normal 50Hz video signal processing are the Tuner/IF, maybe an combfilter, a multistandard colour decoder (e.g. TDA 9141), some picture improvements, like PSI, CTI or Picture Booster and a video backend processor, like TDA 4780.

The easiest way to tune up this concept to a PiP-concept, is to build the system shown in Fig. 1.

Fig.1 Two channel PiP-application in a 50Hz domain

The main signal path is marked as bold lines.

For switching between the main YUV-signals and the YUV-output signals from the PiP-system, a fast video switch has to be installed in the main signal path right before the video backend processor. This fast switch is controlled by the DFB-signal provided by the PiP-Controller SAB 9076/77.

The main signal YUV<sub>main</sub> is detached to provide the input signals for the main acquisition input of the PiP controller. The main acquisition part and the display control part of the PiP-controller are synchronized by the H- and V pulses of the colour decoder of the main signal path. This prevents the system for timing errors between the YUV<sub>main</sub> signals and the YUV<sub>PiP</sub> signals in front of the fast switch TDA 8443A.

The signal processing of the sub signal path contains a source selector and a multistandard decoder. The complexity of the video source selector depends on the amount of signals to be displayed in the PiP-windows. Fig. 1 shows a selection of several signals which are available in most of TV-sets nowadays.

- 1. CVBS/Front is the signal source provided by the Cinch plug at the front of most of the TV sets. It gives you the opportunity to display video signals from a camcorder in playback mode, an in-house video camera, an external video camera of an security system or from a game computer (e.g. Nintendo) in a PiP-window.

- 2. The signal inputs SVHS/Front and SVHS/Back gives you the opportunity to display video signals from SVHS camcorder or normal SVHS recorders in a PiP-window.

- 3. The CVBS/SCART inputs give you the opportunity to display the video signals of several sources, connected by a SCART cable to the TV set in a PiP-window, while the main program is still displayed on the screen. These sources could be:

- \* VCR in playback or search mode, to position the tape, or to find a wanted scene or location on the tape.

- \* SAT receiver, to observe the programs on other channels.

- \* Pay-TV-decoder, to observe the programs in coded channels.

The output signals of the source selector could be normal CVBS-signals or Y/C signals from a SVHS-recorder for example.

The following multistandard colour decoder TDA 8310A is able to recognize and to handle both signal types automatically. The colour decoder for the sub channel delivers YUV signals with full luminance bandwidth for the sub acquisition input of the PiP controller and H- and V-pulses to synchronize the sub acquisition part of the PiP controller.

The PiP controller needs a 2MBit VDRAM (Video - DRAM) to store the data of the main- and sub pictures to be displayed in the PiP-windows. These VDRAM could be a TC528257J from Toshiba or a D482234 LE-70 from NEC. Both types are approved by Philips.

This concept offers you some features listed below:

- 1. The video sources of the sub channel can be displayed in a PiP-window. The PiP window can have three different sizes. The PiP window can be located everywhere on the screen. At the same time the main program is displayed on the whole screen in the background.

- 2. The video sources of the sub channel can be displayed in a PiP-window. At the same time the main program can be displayed in a second PiP window. The PiP windows can have three different sizes. The sizes are set for each window separately. Both PiP windows can be located everywhere on the screen and they may overlap each other. The background is filled with the main program.

- 3. The set shows the same features as 2), but the background is unique coloured.

- 4. The main program can be displayed via the PiP controller on the whole screen in life mode or frozen as a still picture.

- 5. The screen is splitted into two halfs, where one half displays the main program and the other half displays the sub program. Both pictures are horizontally reduced by factor two and have the fully vertical resolution. This mode is especially interesting for TV sets with 16:9 picture tube.

The list above describes only the normal modes. In manual mode there are much more features possible.

### Application Note AN96081

### 2.2 Three channel application in 50Hz domain

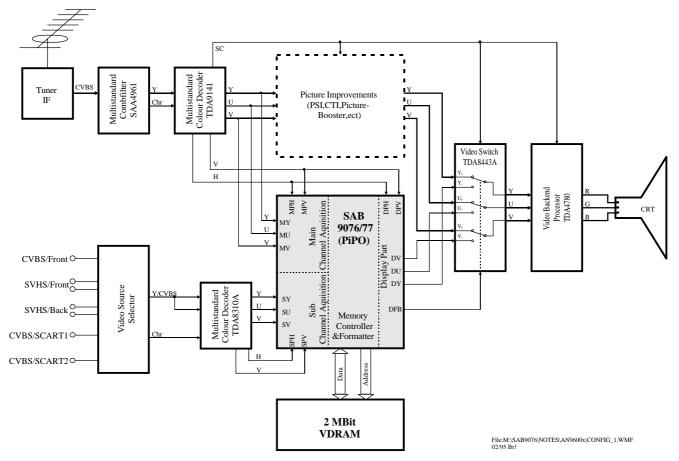

The concept describes under 2.1 operates with only one Tuner/IF section. If the sub channel should display a second broadcasted video signal, the tuner of a associated videorecorder has to be used for this feature. To be really independent from other units, a second tuner/IF section has to be implemented into the TV set. This is shown in the second concept approach in Fig. 2.

Fig.2 Three channel PiP-application in a 50Hz domain

The main signal path supports the main functions of the TV set like sound, pictures on the main screen and deflection, text and so on.

The second tuner gets the same RF input signal as the main tuner. The output of this "PiP-tuner" is a CVBS signal, which is fed into video switching matrix TDA 8540. The other inputs of the switching matrix could be supported from the front panel CVBS input or the SCART input of the back.

The next blocks in this PiP-signal processing chain are the multistandard colour decoders. The main acquisition part of the PiP controller has now its own colour decoder, which delivers the YUV signals and the H- and V-pulses for the main acquisition part.

The configuration of the colour decoder for the sub acquisition part, the PiP controller itself, the VDRAM and the fast switch before the video backend processor is exactly the same as described in chapter 2.1.

Due to the second tuner/IF section and the second colour decoder for the main PiP channel the whole PiP configuration is completely independent from the main signal path of the TV set. The only informations the PiP controller needs from the main signal channel of the TV set are the H- and V- pulses. These pulses have to be fed into

### Application Note AN96081

the display part of the PiP controller, to synchronize the display of the PiP windows and their contents with the deflection of the TV set.

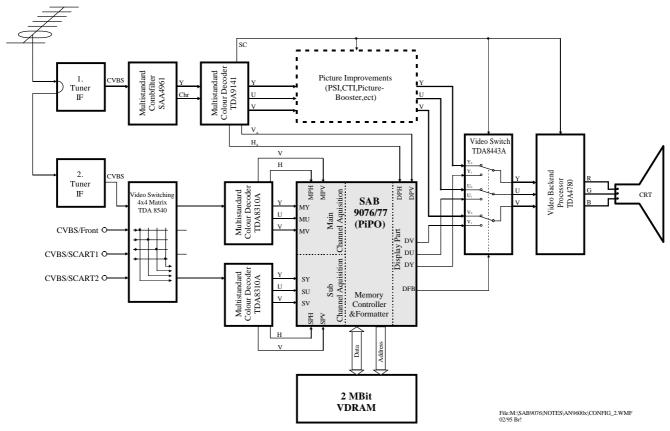

This concept could be extended, if SVHS signal from the front and the back should be included in the PiP signal processing. The following Fig. 3 shows such an approach:

Fig.3 extended three channel PiP-application in a 50Hz domain

For applying the SVHS signals to the multistandard colour decoder, a second video switching matrix is located parallel to the first matrix TDA 8540. While the first matrix lead its output signals to the CVBS1 input of the colour decoders, the second matrix for SVHS signals feeds the CVBS2 and CHR inputs of the colour decoders. If the colour decoder TDA 8310A operates in automatic-mode, it could recognize whether there is a complete CVBS signal or a VBS signal on input CVBS2. If a VBS signal is detected, the internal filters will be switched into SVHS-mode and the device expects a chroma signal on the CHR input.

The selection between the CVBS inputs of the colour decoder is done via a DC-switching voltage, named CTRL in the Fig. 3. The video switching matrix TDA 8540 provide control outputs which are programmable by IIC-bus.

So the complete selection (which SVHS signal to which colour decoder) and the mode control of the colour decoders (normal CVBS-mode or SVHS-mode) can be done via IIC-bus.

### Application Note AN96081

### 2.3 Applications for 100Hz - TV - concepts

The PiP signal processing can be implemented also in 100Hz TV concepts. Based on the former explained concepts, the PiP signal processing joins the main signal path before the 50/100Hz conversion.

Fig.4 PiP signal processing in 100Hz TV concepts Inserting the PiP signals on 50Hz domain

The PiP signal processing shown in Fig. 4 is still the same as explained in chapter 2.2. The display part of the PiP controller is operating in the normal 50Hz domain. Therefore the synchronisation pulses DPH and DPV have to be provided by the main channel colour decoder TDA 9141. They are derived from HA and VA output signals of the TDA 9141.

The fast video signal switch TDA 8443A is positioned in front of the Feature Box for 50 -> 100Hz conversion. This IC is controlled by a DFB pulse with a frequency of 16 kHz (1\*fH).

The feature box needs the H- and V pulses of the main channel colour decoder for synchronisation on the 50Hz domain, too. It provides H- and V pulses and a linelocked clock on the 100Hz domain for devices, which are operating on the 100Hz domain, e.g. the deflection processor TDA 9151B. This device provides a 100Hz sandcastle pulse, to synchronize the video backend processor TDA 4780 in 100Hz mode.

The advantage of this concept is, that all the PiP pictures and their contents are normal video informations for the feature box. So the PiP pictures are included in the signal processing and interpolation of the 50/100Hz conversion. That means the PiP information will also displayed in the A,A\*,B\*,B mode as the video signal of the main signal path.

The disadvantage of this solution is that the PiP pictures can't be switched off, if the feature box is in freeze mode, because the PiP pictures are normal content of the incoming video signal.

### Application Note AN96081

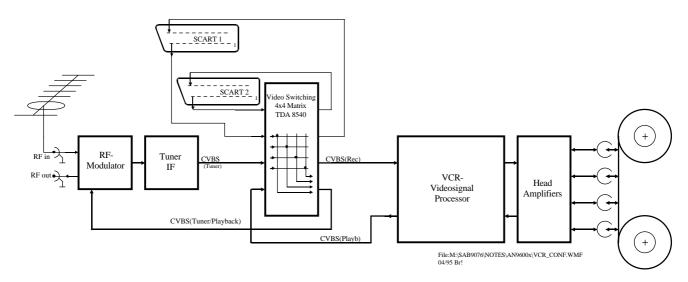

### 2.4 Applications for VCR - concepts

The PiP signal processing concept can also be implemented into VCR concepts. For example, the customers wish to have an overview about the programs available via antenna/cable or satellite during the VCR is in play-back mode.

Due to modern integration technique, the video signal processing in video recorder has become more and more simple. So the complete signal processing can be done with a few ICs, which is shown in the upper part of the following Fig. 5. The added blocks for the PiP signal processing are displayed in more details. It seems, that the expenditure for implementation the PiP concept is large, but that isn't true.

Fig.5 Video signal processing in VCR - concept

The normal signal path inside the VCR video signal processing is shown in bold lines.

The RF input signal is filtered inside the modulator and demodulated to a CVBS signal in the Tuner/IF section. Their output signal is fed into a 4X4 video switching matrix TDA 8540, to select the input signal for the VCR video signal processor. The other available input signals can be the CVBS signals of the SCART inputs coming from a satellite receiver or a pay-TV-decoder for example.

The selected signal [CVBS(Rec)] is processed by the VCR video signal processor and written via the head amplifiers to the tape.

In playback mode the information of the tape is read and processed back to a CVBS signal [see Fig. 5 CVBS(Playb)] by the VCR video signal processor. This signal is lead to the switching matrix again to distribute it to the SCART connectors and the modulator. The modulator converts the CVBS signal back to a RF signal to supply TV sets, which have no SCART inputs.

### Application Note AN96081

The implementation of the PiP signal processing has to fulfil two major requirements:

- 1. The main video signal processing path should be touched as less as possible.

- 2. The implemented PiP signal processing should be as flexible as possible.

The result is shown in Fig. 6.

### Application Note AN96081

The first requirement is fulfilled with insertion of only one fast switch TDA 8443A into main signal path. This fast switch selects between the output video signals of the VCR video signal processor and the PiP signal processing. In fact the PiP CVBS signal is inserted into the CVBS(Playback) signal. The completed signal is fed into the video matrix of the VCR main path, to distribute it to the modulator **and** to the SCART connectors.

The second requirement is fulfilled by the completely parallel signal processing of the PiP path. The kernel of the PiP signal processing is the well known configuration of the two multistandard colour decoder, the PiP controller and the VDRAM.

To insure the independence of the PiP signal processing from the VCR main signal path, the input signals for the colour decoders are selected by an extra video switching matrix. The input signals for this matrix are delivered from the Tuner/IF section, the SCART sockets and the VCR video signal processor.

The selected CVBS signals are lead to the colour decoders and converted into YUV signals. The YUV signals of the main and sub channel will be processed inside the PiP controller.

The main acquisition part is synchronized by the main colour decoder and the sub acquisition part is synchronized by the sub colour decoder. The display part is locked to the main acquisition part in this configuration, but other solutions are possible, too. It always has be ensured, that the display part of the PiP controller is synchronized to that video signal which is actual carried out as the VCR main signal.

The output signals of the PiP controller have to be converted to a CVBS signal first, before they can be inserted into the CVBS(Playback) signal of the VCR video signal processor. This is done by the PAL/NTSC Encoder TDA8501 for example. This device has to be locked to the same H - and V synchronisation pulses as the display part of the PiP controller. The completed CVBS(PiP) signal is connected to the second input of the fast CVBS switch. This switch is controlled by the DFB pulse coming from the PiP controller.

If the PiP controller is switched into OFF state, the DFB pulse has a constant state and the output signal of the VCR video signal processor is connected continuously to the output of this fast switch. In the case of displaying a coloured background together with the PiP pictures, the DFB pulse has the constant opposite state. So the output signal of the VCR video signal processor is blanked.

In normal operation mode the fast switch is toggling between the two input signals. In playback mode the PiP signal CVBS(PiP) is inserted into the video signal coming from tape. If the VCR operates in stop - or tuner mode, the VCR video signal processor must have an EE-mode [CVBS(Rec)=CVBS(Playback)] to ensure the connection of the selected input signal to the first input of the fast switch.

This configuration allows, for example, to display the video signal of the SCART2 connector as the main signal and the tuner-CVBS signal as PiP signal. Both together could be lead to the SCART1 connector as output signal.

As an option Fig. 6 shows the RGB configuration. The output signals of the PiP controller are connected to a second fast switch IC TDA 8443A. This IC operates as an YUV -> RGB matrix only. Its output signals together with the DFB pulse are connected to the RGB and BLANK pins of the SCART1 connector.

This configuration allows the inserting of the PiP signals into a synchronized CVBS signal inside a monitor, which is connected to the SCART1 socket.

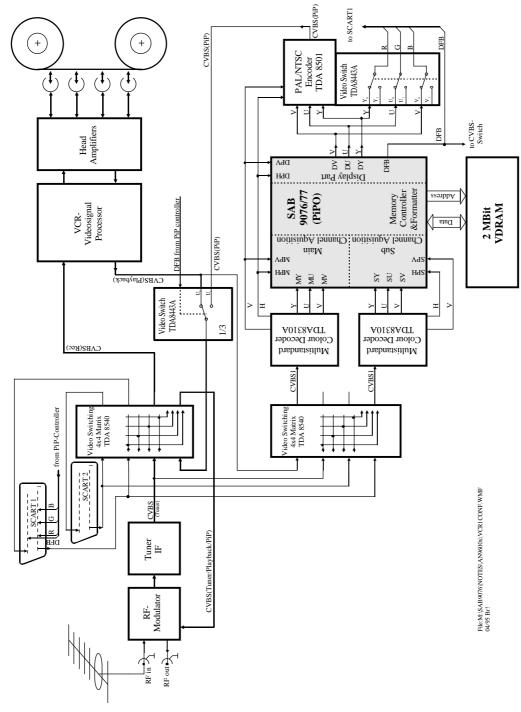

For the case, that the VCR video signal processor couldn't operate in an EE-mode, the location of the CVBS fast switch has to be changed. The varied configuration is shown in Fig. 7.

### Application Note AN96081

Fig.7 Second implementation of PiP signal processing into a VCR - concept

This configuration allows to insert the PiP CVBS signal into a selected incoming CVBS signal from the tuner, SCART1 connector, SCART2 connector or into the CVBS(Playback) signal from the VCR video signal processor. The disadvantage of this concept is, that the combined signal is fed only to the modulator and not to the SCART connectors. This effect could be avoided by adding a third video switching matrix.

### Application Note AN96081

### 2.5 Applications for SAT - Receivers

Modern satellite receivers, especially twin-receivers offer the opportunity to receive two independent satellite signals and distribute them to several devices like TV sets, descrambling (Pay-TV) decoders or VCRs. So these receivers are interesting for the implementation of a PiP signal processing.

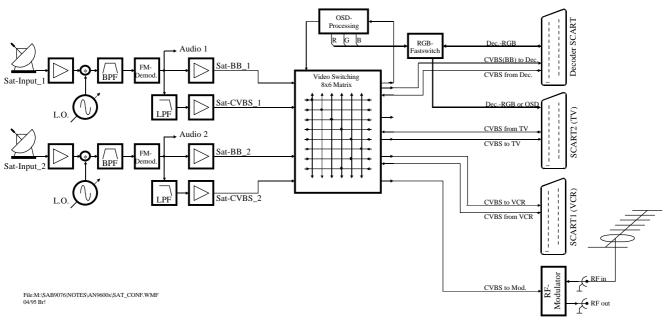

The basic concept of a Twin-Satellite receiver is shown in Fig. 8.

Fig.8 Blockdiagram of Twin-Satellite receiver

A Twin-Satellite receiver has two similar frontends. They convert and demodulate the incoming satellite signals to a normal CVBS signal (Sat-CVBS\_1,2). The second outputs of these frontends are the baseband outputs Sat-BB\_1,2. The baseband signals are not bandwidth limited and contain informations, which are necessary for the descrambling decoders.

All four signals are fed into a video switching matrix.

The video switching matrix delivers the selected baseband signal (Sat-BB\_1,2) to the SCART connector, where the descrambling decoder is connected to. Most of the descrambling decoders give back the decoded TV signal as a normal CVBS signal and as RGB signals. The CVBS signal from the decoder is fed into the matrix to be distributed to the TV-SCART, the VCR-SCART or to the RF-modulator.

The RGB output signals of the decoder are mixed with the RGB signals from the OSD-block and lead to the TV-SCART connector.

The matrix serves also the TV-SCART connector and the VCR-SCART connector with incoming and outgoing CVBS signals.

One of the CVBS signals (Sat-CVBS\_1,2 or CVBS from decoder or CVBS from TV or CVBS from VCR) can be selected for the RF-modulator.

### Application Note AN96081

The implementation of the PiP signal processing has to fulfil again the two major conditions:

- 1. The existing concept of the SAT-receiver should be touched as less as possible.

- 2. The expenditure of the additional circuitry for the PiP signal processing should be small.

These conditions are fulfilled with the concept shown in Fig. 9.

### Application Note AN96081

In this simple application the demodulated satellite input signals (Sat-CVBS-1,2) are connected to the two inputs of one multistandard decoder TDA 8310A of the PiP kernel. This application only uses the main acquisition channel of the PiP controller to display the actual SAT program of either input 1 or input 2. The selection between the inputs of the multistandard decoder (CVBS1 <-> CVBS2) has to be done by a control voltage, issued from a IIC bus device.

The selected input CVBS signal is converted into YUV-signals and the synchronization pulses are generated, too. The YUV signals are processed by the PiP controller and the H- and V-pulses synchronize the main acquisition part. The display part of the PiP controller as well as the PAL/NTSC encoder TDA 8501 will be synchronized by H- and V-pulses derived from the CVBS signal where the CVBS(PiP) signal should be inserted into.

The encoder is necessary to convert the processed YUV signals back to the CVBS domain.

The complete output signal of the PiP kernel [CVBS(PiP)] is lead to a fast CVBS switch TDA 8443A which inserts the CVBS(PiP) signal into a selected CVBS signal, intended to be modulated by the RF-modulator. The fast CVBS switch is controlled by the DFB signal coming from the PiP controller. Every time this signal is active, the switch leads the CVBS(PiP) signal to the RF-modulator.

With this configuration the user can observe the sat-inputs while he's watching a video film of a VCR for example. The monitor he's watching, has to be switched into RF-mode and to the channel, the SAT receiver is transmitting on.

The concept was kept intentionally simple to keep the expenditure as low as possible. The price for the simplicity is less flexibility. To get more flexibility, the system can be extended as shown in Fig. 10.

The extended application has an additional multistandard colour decoder TDA 8310A for the sub acquisition channel and the fast CVBS switch is performed as a double switch. The second colour decoder gives the opportunity to display the two independent satellite input signals at the same time together with a third CVBS signal as background.

In this application the connections between Sat-CVBS1,2 and the inputs of the main/sub colour decoders are fixed. So the input switch control of the main colour decoder is obsolete.

The processed PiP output signals are converted to the CVBS domain by a PAL/NTSC encoder TDA 8501 like in the concept before. The completed signal [CVBS(PiP)] is lead now to two switches which insert the CVBS(PiP) signal into the selected CVBS signal for the RF-modulator and in parallel into the selected CVBS signal for the TV set, connected to the SAT receiver via the SCART2(TV) connector.

# Application Note AN96081

### Application Note AN96081

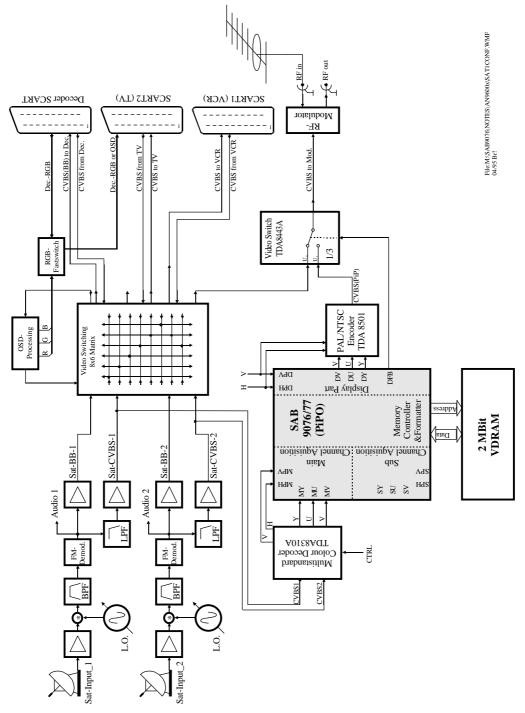

The both concepts described before are able to display only the SAT input signals as PiP pictures in their PiP windows. If more program sources should be available for the PiP processing, the flexibility has to be extended again. This is shown in Fig. 11.

Fig.11 High end application of PiP signal processing in a SAT-receiver concept

### Application Note AN96081

The PiP signal processing is now extended by an additional video switching matrix to select the input CVBS signals for the multistandard decoders of the PiP kernel. With this configuration the two SAT input signals (Sat-CVBS1,2) and the output signals of the descrambling decoder (CVBS from Decoder) and the VCR (CVBS from VCR) can be selected as input signals for the PiP processing.

The backend of the PiP signal processing is still the same as described before.

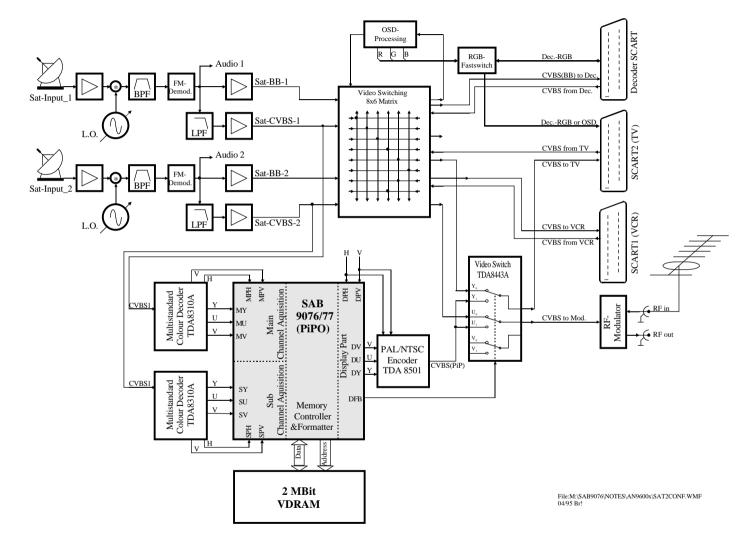

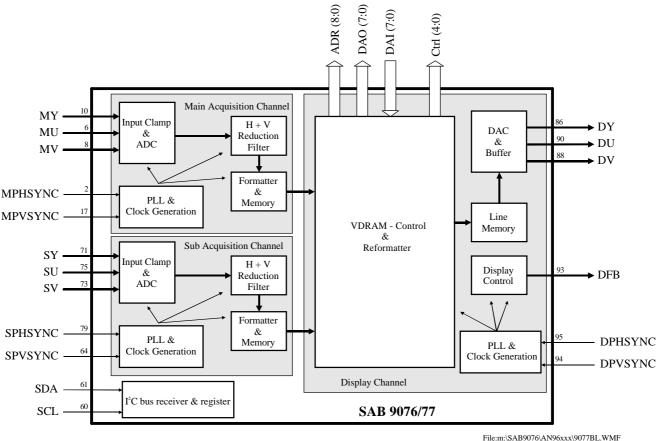

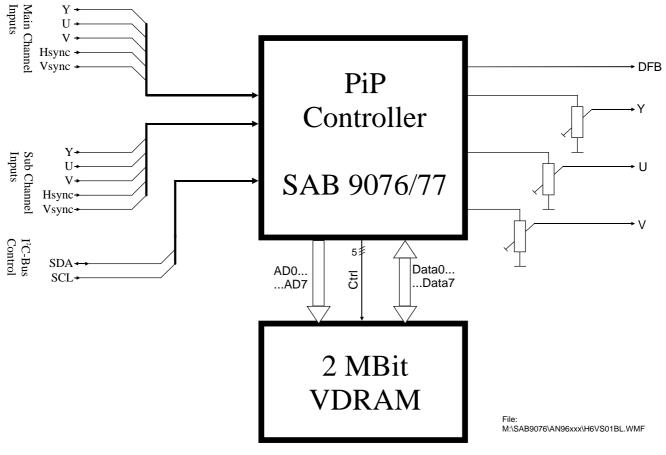

### 3. Short Description of the PiP-Controller SAB 9076/77

In this report only a short description of the PiP controller SAB 9076/77 and it's features are given. A more detailed description is given in the application note AN96041 "Picture-in-Picture Controller SAB 9076".

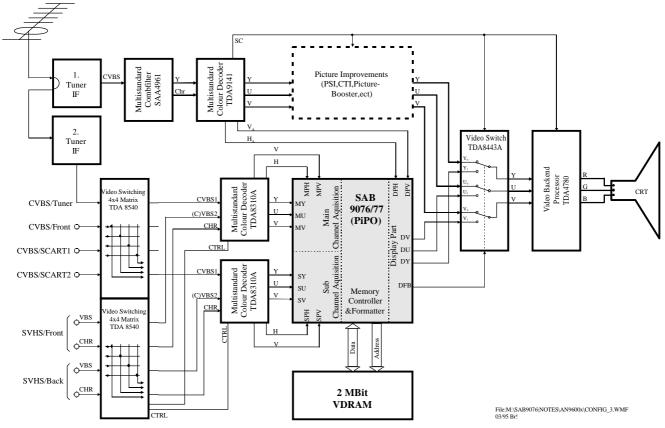

### 3.1 Blockdiagram

The PiP controller consists of three independent major parts:

- 1. Sub channel acquisition part for sampling and filtering the sub channel video signals.

- 2. Main channel acquisition part for sampling and filtering the main channel video signals.

- 3. Display part for providing the processed video data with the correct timing in respect to the display H- and V pulses. The blocks for formatting and reformatting the video data as well as the complete memory controller and the A/D conversion are included in this part, too.

Fig. 12 shows the top shell block diagram of the PiP controller SAB 9076/77.

File:m:\SAB9076\AN96xxx\9077BL.WMF 08/96 Br!

Fig.12 Top shell block diagram of the PiP controller SAB 9076/77

### 3.2 Description of Blocks

The main - and the sub channel acquisition part are identical.

The incoming YUV signals are sampled into the 4:1:1 data format. The bandwidth of the input signals is expected to be limited to 4.5 MHz for the luminance and 1.125 MHz for the chroma difference signals.

The Y input signal is clamped and sampled with a 1728 •  $f_H$  clock (~ 27 MHz). The data stream is then filtered and down sampled to the internal data rate of 864 •  $f_H$  (~13.5 MHz).

The U- and V input are first multiplexed and then sampled with a 432 •  $f_H$  clock (~ 6.75 MHz). Same as the luminance data, they are down sampled to the half pixel rate of 216 • fH (~ 3.375 MHz).

Behind the down sampling the data reduction filters are attached. They reduce the data in horizontal and vertical direction in respect to the desired PiP size. The remaining pixels/line and lines/PiP depend on the selected PiP-size and are listed below in Table 1.

| Condition             | Reduction - Factor |     |     |     |  |  |  |

|-----------------------|--------------------|-----|-----|-----|--|--|--|

| Horizontal reduction  | 1                  | 1/2 | 1/3 | 1⁄4 |  |  |  |

| Pixel per Line        | 672                | 336 | 224 | 168 |  |  |  |

| Vertical reduction    | 1                  | 1/2 | 1/3 | 1⁄4 |  |  |  |

| Lines per PiP in NTSC | 228                | 114 | 76  | 57  |  |  |  |

| Lines per PiP in PAL  | 276                | 138 | 92  | 69  |  |  |  |

### TABLE 1 Pixels and Lines of PiP in respect to desired reduction

The reduced data stream in the 4:1:1 format has to be formatted to meet the data format of the external memory. The complete processed data are stored in an internal line memory and provided to the VDRAM controller.

The complete timing (clock generation, sampling, filtering etc.) is synchronized in horizontal and vertical direction by the applied H- and V pulses [M(S)PHSYNC and M(S)PVSYNC]. M stands for "main channel" and S stands for "sub channel".

With the acquisition fine positioning (I<sup>2</sup>C bus register value) added to a fixed system constant, the start of the acquisition can be controlled in horizontal and vertical direction, independent for each acquisition channel.

The VDRAM controller is responsible for the complete data handling to and from the external memory. This block is a part of the IC's display channel and it's timing is determined by the display control block. The data transmissions between the acquisition parts and the external memory has a different priority than the data transmission from the external memory to the display part of the IC.

Providing correct data to display part has always the highest priority. The necessary processing time of the remaining blocks of the display part like reformatter, upsampling or D to A conversion has to be taken into account. In the time slots, where no data have to be fetched from the external memory, the provided data from the acquisition part can be written to the external memory. Due clever data handling a synchronization between non synchron video sources of the main- and the sub acquisition channels and the timing of the environment, the PiP application is implemented in, is obtained.

The data read back from the memory have to be reformatted to the 4:1:1 format. The data stream has a pixel rate of 864 • f<sub>H(Display)</sub> (~ 13.5 MHz). This data stream is fed to the line memory.

The VDRAM controller gets it's start- and control signals from the display PLL and the display controller. These blocks are locked to the timing raster of the environment, the PiP application is implemented in. The synchronization is obtained by the attached H- and V pulses DPHSYNC and DPVSYNC.

The complete address generation for both, writing the processed data to the memory and reading back data for the display part as well as control signal generation for the external memory are included in the VDRAM controller.

The reformatted data stream is intermediate stored in the line memory of the display part to provide the data for

### Application Note AN96081

the upsampling stage. The upsampling stage generates a pixel rate of  $1728 \cdot f_{H(Display)}$  (~ 27MHz) by interpolation.

This data stream is converted back to the analog domain and buffered by three output buffer stages. The display controller generates the output signal DFB, which indicates when the output signals DY, DU and DV have valid video signals. Borders of PiP pictures are valid video signals, too.

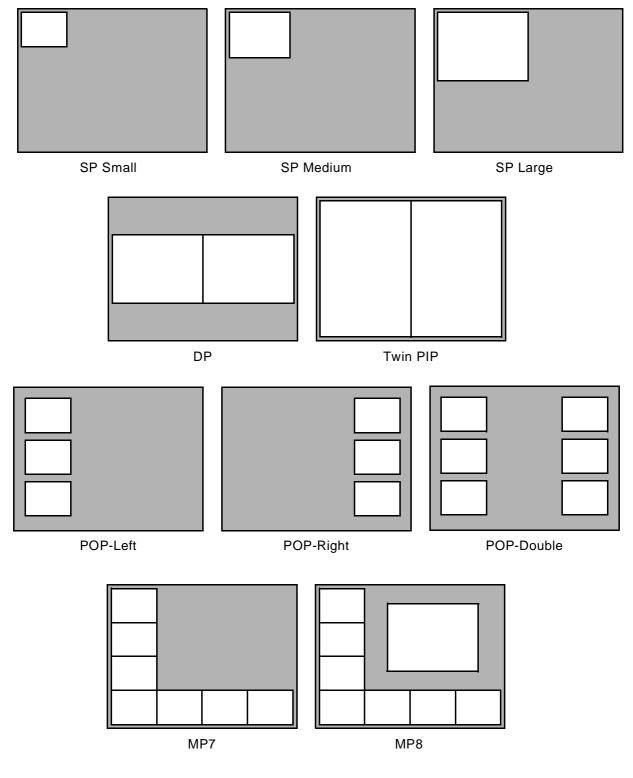

### 3.3 PiP modes

The architecture of the PiP controller allows a very flexible controlling of the two acquisition- and the display channel, independent of each other. So a lot of several modes are possible, but a subset of seven modes is fixed and can easily be set by  $I^2C$  bus. The standard PiP modes with their associated presettings are listed below in Table 2.

| PIP Modes     |                  |      | Reduction Factors |      |              |      | PiP positioning |       |              |       |  |

|---------------|------------------|------|-------------------|------|--------------|------|-----------------|-------|--------------|-------|--|

|               | FIF WOUES        |      | Sub Channel       |      | Main Channel |      | Sub Channel     |       | Main Channel |       |  |

| Name Figure M |                  | Mode | Hred              | Vred | Hred         | Vred | SDhfp           | SDvfp | MDhfp        | MDvfp |  |

| SP            | SP Small         | 0000 | 1/4               | 1/4  | -            | -    | -               | -     | -            | -     |  |

| SP            | SP Medium        | 0000 | 1/3               | 1/3  | -            | -    | -               | -     | -            | -     |  |

| SP            | SP Large         | 0000 | 1/2               | 1/2  | -            | -    | -               | -     | -            | -     |  |

| SP            | SP Small         | 0000 | -                 | -    | 1/4          | 1/4  | -               | -     | -            | -     |  |

| SP            | SP Medium        | 0000 | -                 | -    | 1/3          | 1/3  | -               | -     | -            | -     |  |

| SP            | SP Large         | 0000 | -                 | -    | 1/2          | 1/2  | -               | -     | -            | -     |  |

| DP            | DP               | 0000 | 1/2               | 1/2  | 1/2          | 1/2  | 03h             | 46h   | 57h          | 46h   |  |

| DP            | Twin PIP         | 1001 | 1/2               | 1/1  | 1/2          | 1/1  | 03h             | 05h   | 57h          | 05h   |  |

| MP3L          | POP-Left         | 0010 | 1/4               | 1/4  | -            | -    | 08h             | 10h   | -            | -     |  |

| MP3R          | POP-Right        | 0010 | -                 | -    | 1/4          | 1/4  | -               | -     | 72h          | 10h   |  |

| MP3D          | POP-Double       | 0010 | 1/4               | 1/4  | 1/4          | 1/4  | 08h             | 10h   | 72h          | 10h   |  |

| MP7           | POP-Double       | 0011 | 1/4               | 1/4  | -            | -    | 03h             | 05h   | -            | -     |  |

| MP8           | MP7              | 0011 | 1/4               | 1/4  | 1/2          | 1/2  | 03h             | 05h   | 44h          | 20h   |  |

| MP4           | Quatro           | 0001 | 1/2               | 1/2  | 1/2          | 1/2  | 03h             | 05h   | 03h          | 77h   |  |

| MP9           | MP9              | 0100 | 1/3               | 1/3  | 1/3          | 1/3  | 03h             | 05h   | 51h          | 3Bh   |  |

| MP16          | MP16             | 0101 | 1/4               | 1/4  | 1/4          | 1/4  | 03h             | 05h   | 03h          | 05h   |  |

| MP16          | MP16 Mix         | 0110 | 1/4               | 1/4  | 1/4          | 1/4  | 03h             | 05h   | 03h          | 77h   |  |

| FFS           | Full Field Still | 0000 | 1/1               | 1/1  | -            | -    | 03h             | 05h   | -            | -     |  |

| FFS           | Full Field Still | 1000 | -                 | -    | 1/1          | 1/1  | -               | -     | 03h          | 05h   |  |

| MAN           | Manual           | X111 | х                 | х    | х            | х    | х               | х     | х            | х     |  |

### TABLE 2 PIP Modes and presettings

The abbreviations are:

### TABLE 3 Abbreviation of standard PiP modes

| Abbreviation | Meaning            | Remark                                             |

|--------------|--------------------|----------------------------------------------------|

| SP(S/M/L)    | Single PiP         | S = small (1/4); M = medium (1/3); L = large (1/2) |

| DP           | Double PiP         | two large PiP's on coloured background             |

| POP          | Picture on Picture |                                                    |

| MP(n)        | Multi - PiP        | (n) = number of PiPs (3,4,7,8,9 or 16)             |

### Application Note AN96081

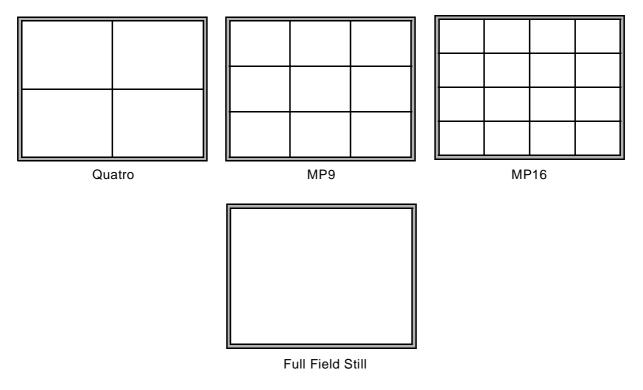

The layouts of the several PiP modes are shown in the following Fig. 13 and Fig. 14 .

Fig.13 Pip modes 1

### Application Note AN96081

Fig.14 Pip modes 2

The standard PiP modes are selected by the corresponding mode bits of the I2C bus register. To display the PiP pictures in the arrangement shown above, the correct setting of the main/sub display positioning bits is necessary. The required values are listed in Table 2 in the right four columns. The basics of PiP picture positioning is explained in the chapter below.

### 3.4 Background- and PiP positioning

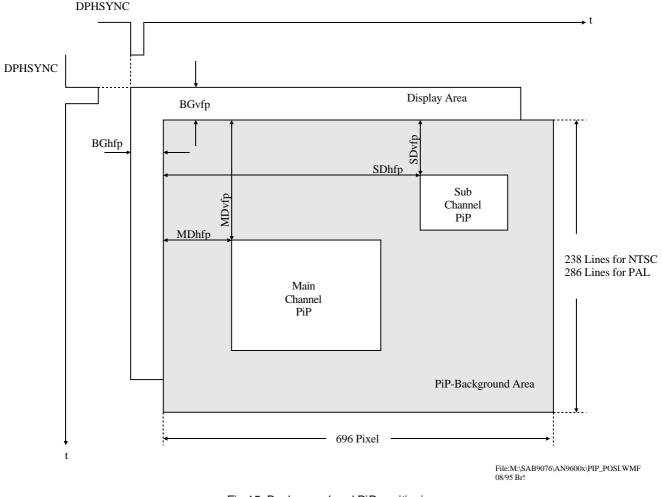

The PiP background is an area of 696 pixel for both PAL and NTSC and 238 lines for NTSC or 286 lines for PAL. The environment, the PiP application is implemented in has a display area which is determined by it's H- and V pulses. These synchronization pulses (DPHSYNC & DPVSYNC) are fed to the display part of the PiP controller, too and determine the basic display area of the PiP controller. This is shown in Fig. 15.

The PiP background area is locked to the display area and can be shifted in horizontal and vertical direction. The shift is determined by the values in the corresponding I<sup>2</sup>C bus registers BGhfp and BGvfp. The maximum shifting range is 64 pixel in horizontal and 36 lines in vertical direction.

Inside the background area the PiP pictures are defined. Their starting points (upper left corner) are defined by the values in the I<sup>2</sup>C registers MDhfp and MDvfp for the main channel and SDhfp and SDvfp for the sub channel. The PiP pictures may overlap, but they can't leave the background area.

Normally the background is transparent, so the life picture of the TV set is visible. Then the PiP pictures lay over the TV-set's life picture.

The background also can be coloured with several colours. In this case the TV-set's life picture is blanked and the PiP pictures occur on an unique background.

### Application Note AN96081

### Fig.15 Background and PiP positioning

### 3.5 I<sup>2</sup>C-Registers

The PiP device SAB 9076/77is fully controllable by I<sup>2</sup>C bus. The device address can be selected between  $2C_{HEX}$  and  $2E_{HEX}$  by hardware configuration. For default the I'C bus address is  $2C_{HEX}$ . The evaluation- and control software is written for the I2C bus address  $2C_{HEX}$ , too. In the evaluation- and control software the address is fixed and can't be changed.

In normal operation mode the subadresses  $00_{HEX}$  to  $18_{HEX}$  are valid. If the manual mode is selected, the subadresses  $20_{HEX}$  to  $32_{HEX}$  become accessible.

The PiP controller contains a I<sup>2</sup>C bus receiver and can't send any information back to the I<sup>2</sup>C bus master. The data transmission has to be made accordingly to the standard I<sup>2</sup>C bus protocol.

An overview of the I2C bus registers and their content is given in Table 4 .

| Sub     | Data Bytes |                     |                        |                     |                     |                          |                        |                     |  |  |

|---------|------------|---------------------|------------------------|---------------------|---------------------|--------------------------|------------------------|---------------------|--|--|

| Address | Bit 7      | Bit 6               | Bit 5                  | Bit 4               | Bit 3               | Bit 2                    | Bit 1                  | Bit 0               |  |  |

| 00H     | MPIPON     | SPIPON              | MFreeze                | SFreeze             | МСору               | PiPMode <sub>(2:0)</sub> |                        |                     |  |  |

| 01H     | -          | -                   | M1FLD                  | S1FLD               | NiPCoff             | DNonInt                  | MNonInt                | SNonint             |  |  |

| 02H     | DFilt      | FILLOFF             | SMART6                 | SKIP6               |                     | Yth                      | (3:0)                  |                     |  |  |

| 03H     |            | BGhf                | P(3:0)                 |                     |                     | BGvt                     | P(3:0)                 |                     |  |  |

| 04H     |            |                     |                        | SDhi                | <sup>i</sup> P(7:0) |                          |                        |                     |  |  |

| 05H     |            |                     |                        |                     | P(7:0)              |                          |                        |                     |  |  |

| 06H     |            |                     |                        | MDh                 | <sup>fp</sup> (7:0) |                          |                        |                     |  |  |

| 07H     |            |                     |                        | MDv                 | <sup>f</sup> p(7:0) |                          |                        |                     |  |  |

| 08H     | MDRe       | dH <sub>(1:0)</sub> | MDRe                   | dV <sub>(1:0)</sub> | SDRe                | dH <sub>(1:0)</sub>      | SDRe                   | dV <sub>(1:0)</sub> |  |  |

| 09H     | MARe       | dH <sub>(1:0)</sub> |                        | dV <sub>(1:0)</sub> | SARe                | edH(1:0) SARedV(1:0)     |                        |                     |  |  |

| 0AH     |            | MAhi                | P(3:0)                 |                     |                     | SAhf                     | P(3:0)                 |                     |  |  |

| 0BH     |            |                     |                        | SAvf                | P(7:0)              |                          |                        |                     |  |  |

| 0CH     |            |                     |                        | MAvt                | p(7:0)              |                          |                        |                     |  |  |

| 0DH     |            |                     | el(3:0)                |                     |                     | SLse                     | el (3:0)               |                     |  |  |

| 0EH     |            | MBse                | <sup>el</sup> (3:0)    |                     |                     | SBse                     | <sup>el</sup> (3:0)    |                     |  |  |

| 0FH     |            | Bhsiz               | .e(3:0)                |                     |                     | Bvsiz                    | <u>ze(3:0)</u>         |                     |  |  |

| 10H     | -          | SBON                | SBbi                   | <sup>rt</sup> (1:0) | -                   |                          | SBcol <sub>(2:0)</sub> |                     |  |  |

| 11H     | -          | SBSON               |                        | ort(1:0)            | -                   |                          | SBScol2(2:0)           |                     |  |  |

| 12H     | -          | MBON                | MBb                    | <sup>rt</sup> (1:0) | -                   | MBcol <sub>(2:0)</sub>   |                        |                     |  |  |

| 13H     | -          | MBSON               |                        | ort(1:0)            | -                   | MBScol(20)               |                        |                     |  |  |

| 14H     | -          | BGON                | BGb                    | <sup>rt</sup> (1:0) | -                   | BGcol <sub>(2:0)</sub>   |                        |                     |  |  |

| 15H     | -          | -                   | -                      | SVfilt              | SUVPol              | SVSPol                   | SH <sub>sync</sub>     | SFPol               |  |  |

| 16H     | -          | -                   | -                      | MVfilt              | MUVPol              | MVSPol                   | MH <sub>sync</sub>     | MFPol               |  |  |

| 17H     |            |                     | FBdel <sub>(2:0)</sub> |                     | DUVPol              | DVSPol                   | DH <sub>sync</sub>     | DFPol               |  |  |

| 18H     |            | Pedes               | stV <sub>(3:0)</sub>   |                     |                     | Pedes                    | stU <sub>(3:0)</sub>   |                     |  |  |

### TABLE 4 Overview of $I^{2}C$ bus registers for normal operation modes

If the manual mode is selected, more PiP modes become available and the I<sup>2</sup>C bus registers  $20_{\text{HEX}}$  to  $32_{\text{HEX}}$  become accessible. An overview over this registers is given in Table 5.

| Sub     | Data Bytes                                                                                      |                         |       |                     |                        |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

|---------|-------------------------------------------------------------------------------------------------|-------------------------|-------|---------------------|------------------------|---------------------|------------------------|---------------------|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------------------------|--|------|--------|

| Address | Bit 7                                                                                           | Bit 6                   | Bit 5 | Bit 4               | Bit 3                  | Bit 2               | Bit 1                  | Bit 0               |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 20H     | PRIO                                                                                            | DPal                    | MPal  | SPal                | MVRpN <sub>(1:0)</sub> |                     | MVRpN <sub>(1:0)</sub> |                     | MVRpN <sub>(1:0)</sub> |  | MVRpN <sub>(1:0)</sub> |  | MVRpN <sub>(1:0)</sub> |  | MVRpN <sub>(1:0)</sub> |  | MVRpN <sub>(1:0)</sub> |  | MVRpN <sub>(1:0)</sub> |  | MVRpN <sub>(1:0)</sub> |  | MVRpN <sub>(1:0)</sub> |  | MVRpN <sub>(1:0)</sub> |  | SVRp | N(1:0) |

| 21H     | MHRpO3 <sub>(1:0)</sub> MHRpO2 <sub>(1:0)</sub> MHRpO1 <sub>(1:0)</sub> MHRpO0 <sub>(1:0)</sub> |                         |       |                     |                        |                     |                        | O0 <sub>(1:0)</sub> |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 22H     | MHRpN3 <sub>(1:0)</sub> MHRpN2 <sub>(1:0)</sub> MHRpN1 <sub>(1:0)</sub> MHRpN0 <sub>(1:0)</sub> |                         |       |                     |                        |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 23H     |                                                                                                 | MHPic(7:0)              |       |                     |                        |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 24H     |                                                                                                 |                         |       | MVP                 | ic <sub>(7:0)</sub>    |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 25H     |                                                                                                 |                         |       | MHDi                | s0 <sub>(7:0)</sub>    |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 26H     |                                                                                                 |                         |       | MHDi                | s1 <sub>(7:0)</sub>    |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 27H     |                                                                                                 | MHDis2 <sub>(7:0)</sub> |       |                     |                        |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 28H     |                                                                                                 | MHDis3 <sub>(7:0)</sub> |       |                     |                        |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 29H     |                                                                                                 |                         |       | MVD                 | is(7:0)                |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 2AH     |                                                                                                 | 03 <sub>(1:0)</sub>     |       | 02 <sub>(1:0)</sub> |                        | 01 <sub>(1:0)</sub> |                        | 00 <sub>(1:0)</sub> |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 2BH     | SHRp                                                                                            | N3 <sub>(1:0)</sub>     | SHRp  | N2 <sub>(1:0)</sub> | SHRp                   | N1 <sub>(1:0)</sub> | SHRp                   | N0 <sub>(1:0)</sub> |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 2CH     |                                                                                                 | SHPic <sub>(7:0)</sub>  |       |                     |                        |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 2DH     |                                                                                                 | SVPic(7:0)              |       |                     |                        |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 2EH     |                                                                                                 |                         |       | SHDis               | s0 <sub>(7:0)</sub>    |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 2FH     |                                                                                                 |                         |       |                     | s1 <sub>(7:0)</sub>    |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 30H     |                                                                                                 |                         |       | SHDis               | s2 <sub>(7:0)</sub>    |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 31H     |                                                                                                 |                         |       |                     | s3 <sub>(7:0)</sub>    |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |

| 32H     |                                                                                                 |                         |       | SVDi                | s(7:0)                 |                     |                        |                     |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |                        |  |      |        |